Altera HyperTransport MegaCore Function User Manual

Page 54

3–28

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

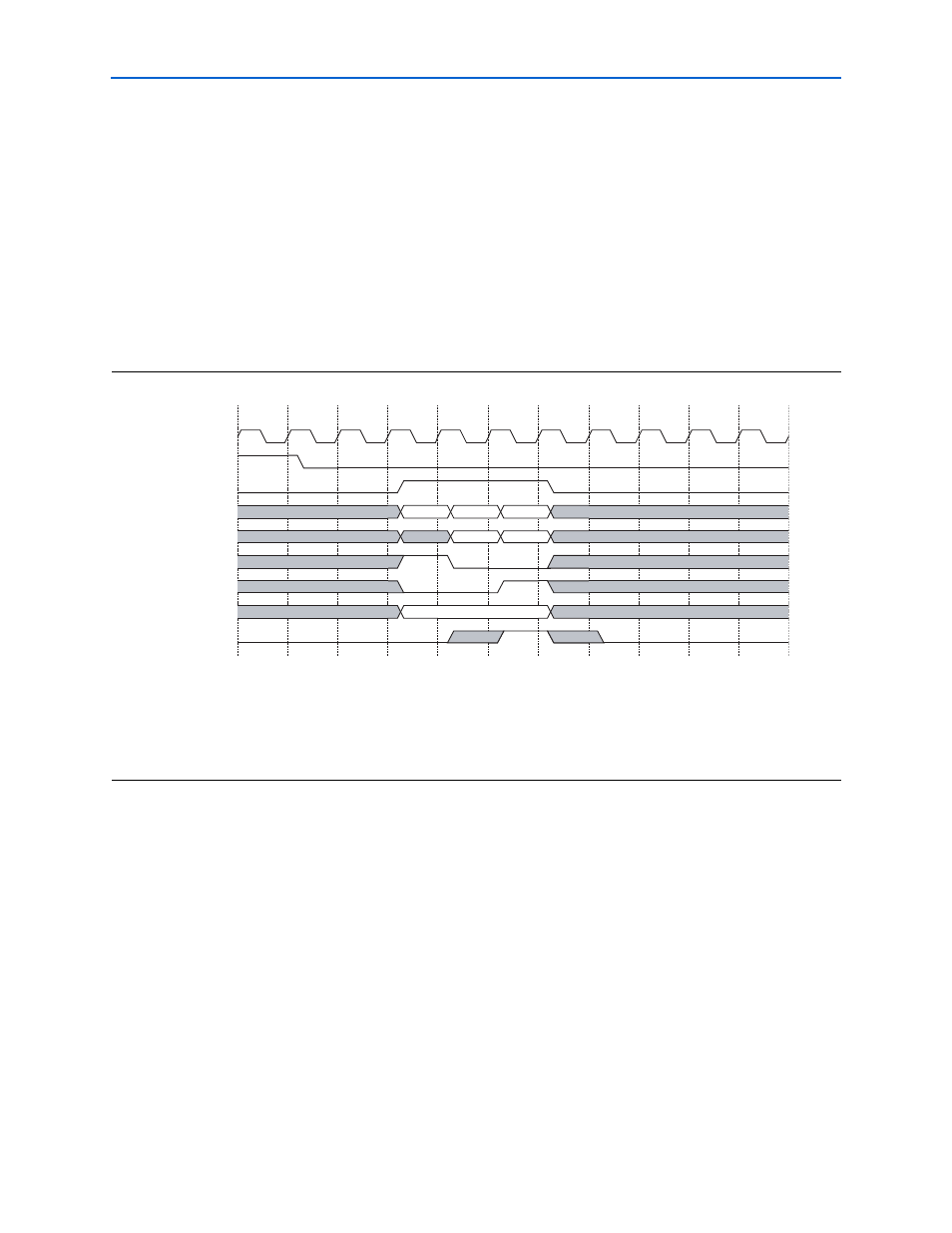

Internally, the HyperTransport MegaCore writes to the Tx response Buffer to write

CSR access responses as well as end-chain responses. To do so, it deasserts

TxRDav_o

so that the user-side application does not write to the buffer at the same time. By

default, it allows one clock cycle after the deassertion of

TxRDav_o

to accept further

writes from the user side, however, the time that user writes are allowed can be

increased by setting the

TxRDavToSopDelay

configuration parameter to a higher

value. This implementation only applies to the Tx response buffer. The Tx posted and

non-posted buffers deassert

Dav_o

only in response to the user writing a packet.

shows the deassertion of

TxRDav_o

and a subsequent user attempt to

write to the Tx response buffer with the

TxRDavToSopDelay

parameter set to the

default value of one.

Figure 3–18. HyperTransport MegaCore Function Internal Deassertion of TxRDav_o Timing Diagram

Notes to

:

(1) In this example,

TxRDatEna_i

is asserted two clock cycles after

Dav_o

is deasserted due to an internal use of the Tx response buffer

(

TxRDatEna_i

was not asserted). This Tx buffer write is deasserted due to a conflict with the internal usage.

(2)

TxRDat_o[63:32]

is not valid in this example because the command is only a read response.

(3)

TxRWrRjct_o

is asserted because

TxRDatEna_i

was asserted with

TxRDav_o

. The exact cycle in which

TxRWrRjct_o

is asserted

varies due to internal buffer conditions.

2

3

4

5

6

7

9

10

RefClk

TxRDav_o

8

1

TxRDatEna_i

TxRDat_i[31:0]

TxRDat_i[63:32]

TxRSop_i

TxREop_i

TxRWrRjct_o

TxRMty_i[2:0]

11

(1)

RdResp

DW0

DW2

DW1

DW3

0b000

(2)

TxRDavToSopDelay=1 (Default)

(3)