Table 3–18 – Altera HyperTransport MegaCore Function User Manual

Page 62

3–36

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

Revision ID (Actual Offset 0x4C)

This register shows the revision of the specification used to design the link interface.

This register is hardwired with 0x13.

Link Frequency Registers (Actual Offsets 0x4D, 0x51)

There are two registers of this type, one for each link. In the HT specification this

register is intended to control the frequency of the link transmit clock. However in the

HyperTransport MegaCore function, the link transmit frequency is always four times

the

RxLnkClkD4

frequency (or when using the Shared Ref/Tx Clock option it is four

times

RefClk

) and the value of this register has no effect inside the MegaCore

function.

1

This register is a read/write register for compatibility with configuration software.

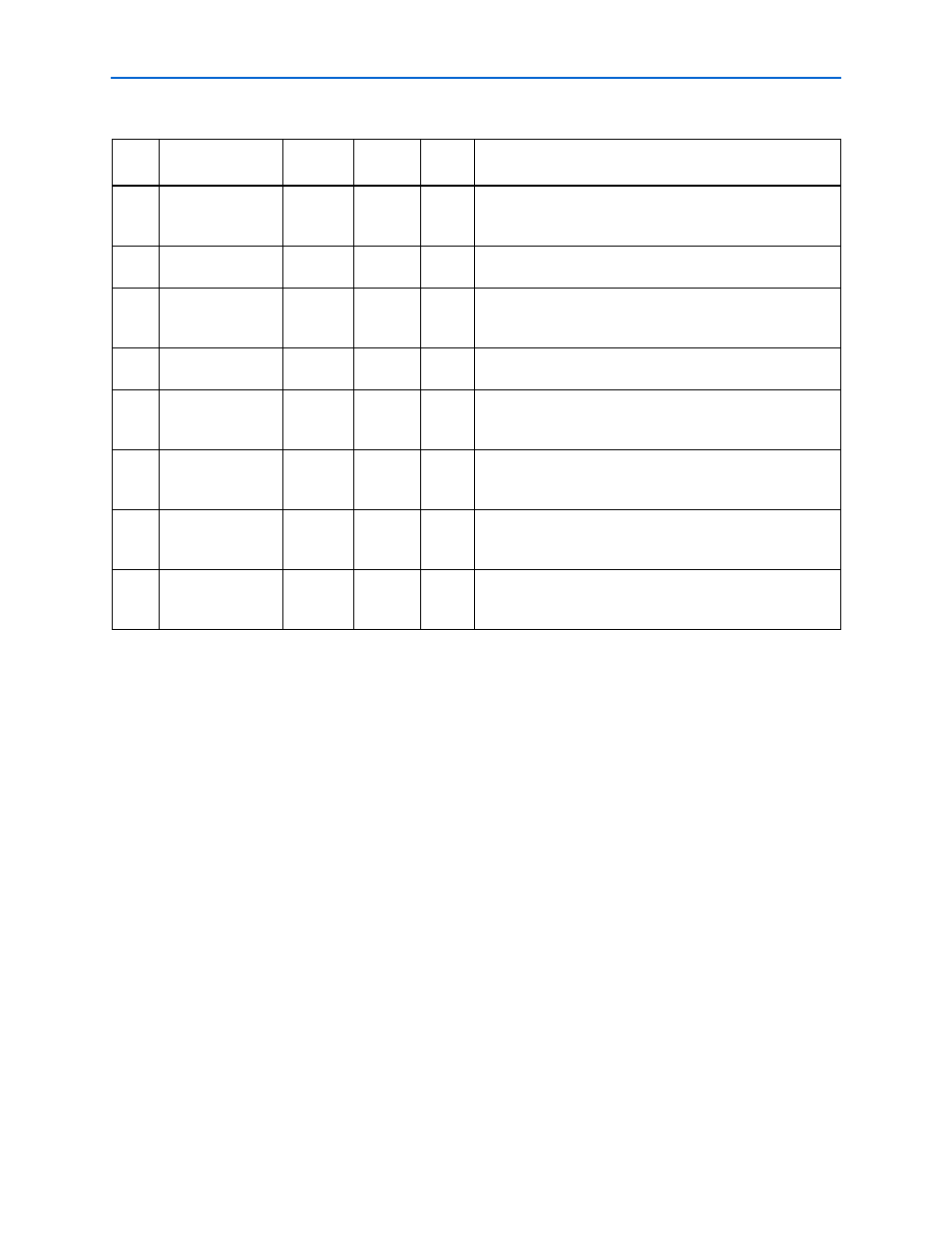

Table 3–18. HT Capability Link Configuration Register Bits Offset: Capability Pointer + 0x06 (Actual Offset: 0x46)

Bits

Name

Register

Type

Default

Reset

Used

Description

2:0

Max Link Width In

R/O

0

N/A

Indicates the maximum width of the incoming side of the

HyperTransport MegaCore function. The value is hardwired

to 000 to indicate an 8-bit maximum.

3

Double Word Flow

Control In

R/O

0

N/A

Indicates that the device is capable of double word-based

data buffer flow control. This bit is hardwired to zero.

6:4

Max Link Width

Out

R/O

0

N/A

Indicates the maximum width of the Tx port of the

HyperTransport MegaCore function. This bit is hardwired to

indicate 8 bits.

7

Double Word Flow

Control Out

R/O

0

N/A

Indicates that Tx is capable of double word flow control. This

bit is hardwired to zero.

10:8

Link Width In

R/O

0

N/A

Indicates the actual width used by the link. This bit is

hardwired to 000 because the MegaCore function does not

have an automatic sizing module.

11

Double Word Flow

Control In Enable

R/O

0

N/A

This bit indicates whether the double word flow control mode

will be enabled. This bit is hardwired to zero because the

MegaCore function does not provide this mode.

14:12 Link Width Out

R/O

0

N/A

Indicates the actual width used by the link. This bit is

hardwired to 000 because the MegaCore function does not

have automatic sizing module.

15

Double word Flow

control Out Enable

R/O

0

N/A

This bit indicates whether the double word flow control mode

will be enabled. This bit is hardwired to zero because the

MegaCore function does not provide this mode.