Altera HyperTransport MegaCore Function User Manual

Page 64

3–38

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

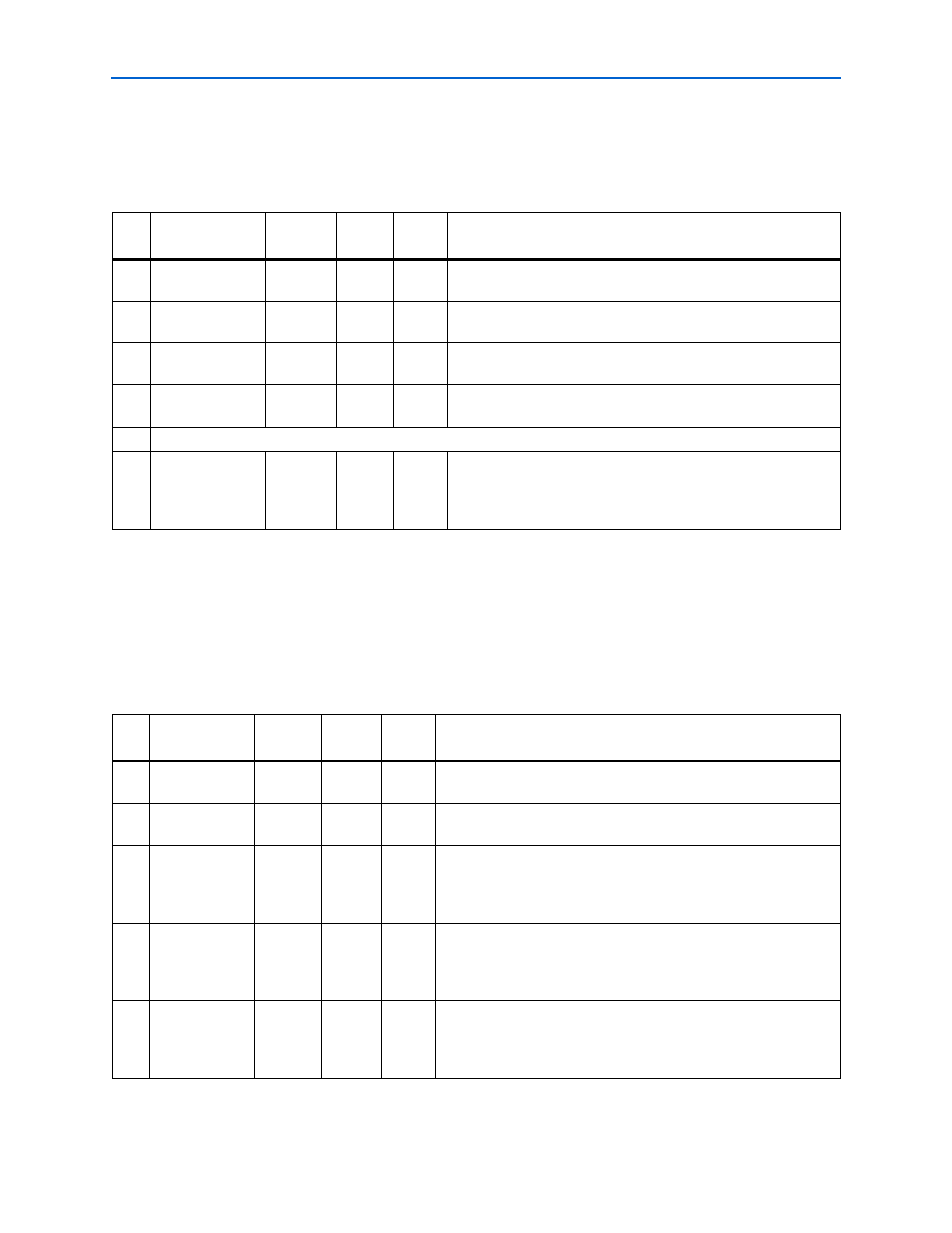

Feature Capability Register (Actual Offset 0x50)

This register indicates which optional features the device supprts.

describes the HT capability feature capability register.

Enumeration Scratch Pad Register (Actual Offset 0x54)

This register is not implemented in the HyperTransport MegaCore function. It is

hardwired to zero.

Error Handling Register (Actual Offset 0x56)

shows the HT capability error handling register bits.

Table 3–22. HT Capability Feature Capability Register Bits Offset: CapabilityPointer + 0x10 (Actual Offset: 0x50)

Bits

Name

Register

Type

Default

Reset

Used

Description

0

Isochronous

Mode

R/O

0

N/A

Indicates that the HyperTransport MegaCore function is not

capable of isochronous mode.

1

LDTSTOP#

R/O

0

N/A

Indicates that the HyperTransport MegaCore function does not

support LDTSTOP# protocol.

2

CRC Test Mode

R/O

0

N/A

Indicates that the HyperTransport MegaCore function does not

support CRC test mode.

3

Extended CTL

Time Required

R/O

0

N/A

Indicates that the HyperTransport MegaCore function does not

require extended CTL time.

6:4

Reserved

7

Extended

Register Set

R/O

1

N/A

Indicates that the HyperTransport MegaCore function implements

the extended error handling register. It does not implement the

enumeration scratch pad register or the memory base/limit upper

registers.

Table 3–23. HT Capability Error Handling Register Bits Offset: Capability Pointer + 0x16 (Actual Offset: 0x56) (Part 1 of 2)

Bits

Name

Register

Type

Default

Reset

Used

Description

0

Protocol Error

Flood Enable

R/W

0

Warm

When set, this bit results in a sync flood when a protocol error is

detected

1

Overflow Error

Flood

R/W

0

Warm

When set, this bit results in a sync flood when an overflow error is

detected.

2

Protocol Error

Fatal Enable

R/O

0

N/A

When set, this bit results in a fatal error interrupt whenever the

protocol error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

3

Overflow Error

Fatal Error

R/O

0

N/A

When set, this bit results in a fatal error interrupt whenever the

overflow error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

4

End of Chain

Error Fatal

Enable

R/O

0

N/A

When set, this bit results in a fatal error interrupt whenever the end-

chain error bit is asserted. This bit is hardwired to zero because the

HyperTransport MegaCore function does not support error

interrupts.