Altera HyperTransport MegaCore Function User Manual

Page 65

Chapter 3: Specifications

3–39

HyperTransport MegaCore Function Specification

© November 2009

Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

Memory Base/Limit Upper Registers (Actual Offset 0x58)

These registers are defined for bridge functions and are hardwired to zero.

5

Response Error

Fatal Enable

R/O

0

N/A

When set, this bit results in a fatal error interrupt whenever the

response error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

6

CRC Error Fatal

Enable

R/O

0

N/A

When set, this bit results in fatal error interrupt whenever one of the

CRC error bits is asserted. This bit is hardwired to zero because the

HyperTransport MegaCore function does not support error

interrupts.

7

System Error

Fatal Enable

R/O

0

N/A

This bit is for host interfaces only.

8

Chain Fail

R/O

0

Warm

This bit is set if a sync flood is detected or a sync-flood generating

error.

9

Response Error

R/C

0

Cold

This bit indicates that the link has received a response error.

10

Protocol Error

NonFatal Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever the

protocol error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

11

Overflow Error

Non-Fatal

Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever

overflow error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

12

End of Chain

Error Non-Fatal

Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever end-

of-chain error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

13

Response Error

Non-Fatal

Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever the

response error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

14

CRC Error

Non-Fatal

Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever any

of the CRC error bits are asserted. This bit is hardwired to zero

because the HyperTransport MegaCore function does not support

error interrupts.

15

System Error

Non-Fatal

Enable

R/O

0

N/A

When set, this bit results in a nonfatal error interrupt whenever the

response error bit is asserted. This bit is hardwired to zero because

the HyperTransport MegaCore function does not support error

interrupts.

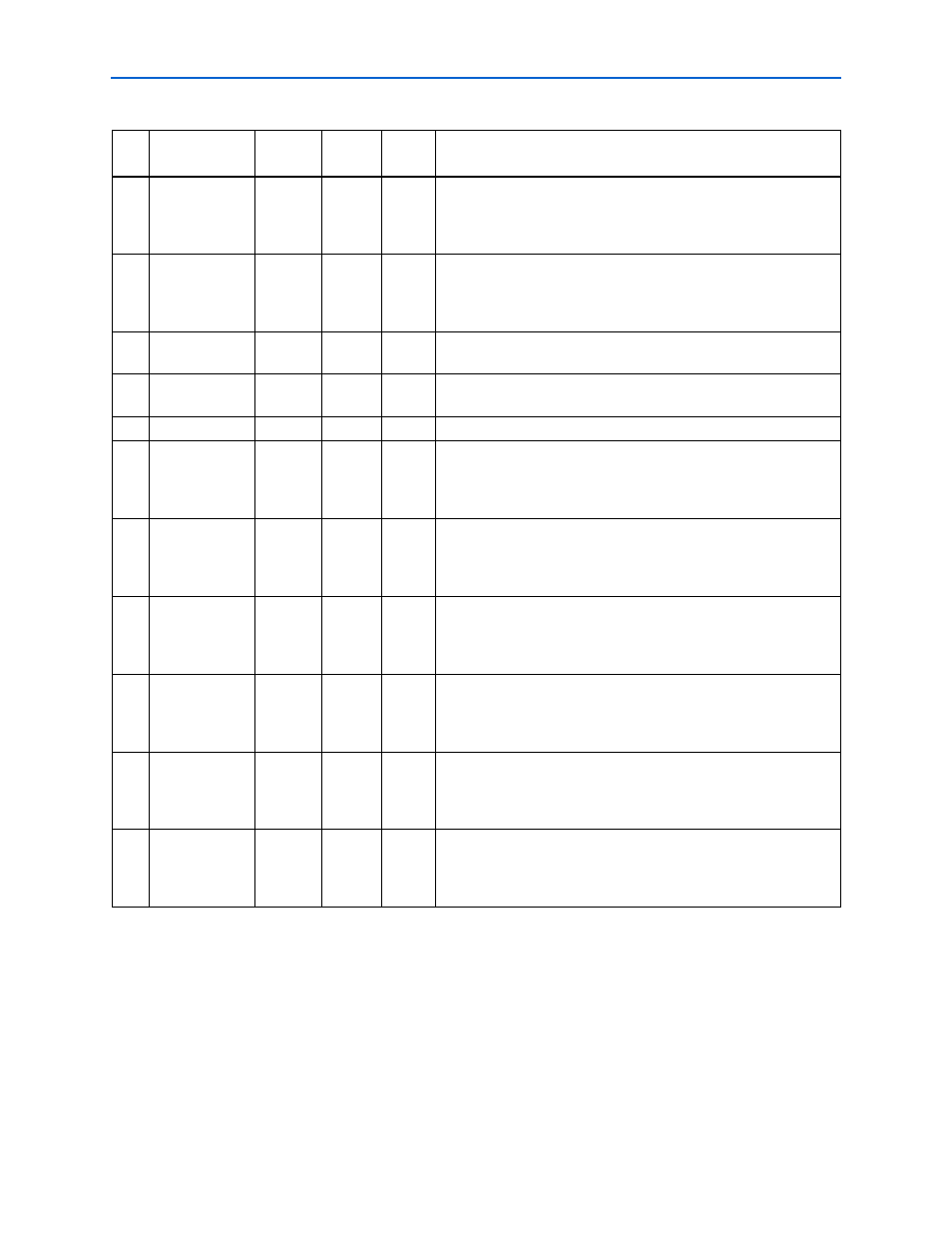

Table 3–23. HT Capability Error Handling Register Bits Offset: Capability Pointer + 0x16 (Actual Offset: 0x56) (Part 2 of 2)

Bits

Name

Register

Type

Default

Reset

Used

Description