Altera Stratix IV GX FPGA Development Board User Manual

Page 18

2–10

Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

November 2010

Altera Corporation

FSM_D3

2.5-V

B8

K30

FSM bus data

FSM_D2

2.5-V

A8

J30

FSM bus data

FSM_D1

2.5-V

A9

D34

FSM bus data

FSM_D0

2.5-V

E9

C34

FSM bus data

MAX2_CLK

2.5-V

E1

K32

FSM bus MAX2 clock

MAX2_WEn

2.5-V

F4

T27

FSM bus MAX2 write enable

MAX2_CSn

2.5-V

E2

E34

FSM bus MAX2 chip select

MAX2_OEn

2.5-V

F3

J33

FSM bus MAX2 output enable

MAX2_BEn3

2.5-V

F1

R27

FSM bus MAX2 byte enable 3

MAX2_BEn2

2.5-V

F6

P29

FSM bus MAX2 byte enable 2

MAX2_BEn1

2.5-V

F2

F34

FSM bus MAX2 byte enable 1

MAX2_BEn0

2.5-V

F5

H34

FSM bus MAX2 byte enable 0

FLASH_CLK

2.5-V

C6

AF26

FSM bus flash clock

FLASH_WEn

2.5-V

A4

AT31

FSM bus flash write enable

FLASH_CEn

2.5-V

E6

AU31

FSM bus flash chip enable

FLASH_OEn

2.5-V

B4

AG27

FSM bus flash output enable

FLASH_RDYBSYn

2.5-V

D6

AT32

FSM bus flash ready

FLASH_RESETn

2.5-V

C4

AL30

FSM bus flash reset

FLASH_ADVn

2.5-V

B3

AN31

FSM bus flash address valid

FPGA_CONFIG_D7

2.5-V

D1

R34

FPGA configuration data

FPGA_CONFIG_D6

2.5-V

E5

R35

FPGA configuration data

FPGA_CONFIG_D5

2.5-V

D2

W26

FPGA configuration data

FPGA_CONFIG_D4

2.5-V

E4

V27

FPGA configuration data

FPGA_CONFIG_D3

2.5-V

C3

P34

FPGA configuration data

FPGA_CONFIG_D2

2.5-V

E3

N35

FPGA configuration data

FPGA_CONFIG_D1

2.5-V

C2

W29

FPGA configuration data

FPGA_CONFIG_D0

2.5-V

D3

W30

FPGA configuration data

FPGA_DCLK

2.5-V

H4

AR11

FPGA configuration clock

FPGA_nSTATUS

2.5-V

H3

AW35

FPGA configuration ready

FPGA_nCONFIG

2.5-V

T2

AW36

FPGA configuration active

FPGA_CONF_DONE

2.5-V

J1

AV35

FPGA configuration done

SENSE_SCK

2.5-V

L5

AE28

Power monitor SPI clock

SENSE_SDI

2.5-V

M3

J35

Power monitor SPI data in

SENSE_SDO

2.5-V

L4

V28

Power monitor SPI data out

SENSE_CS0n

2.5-V

N1

AB31

Power monitor 0 chip select

SENSE_CS1n

2.5-V

L3

H35

Power monitor 1 chip select

SENSE_ADN_F0

2.5-V

N2

G35

Power monitor frequency

SENSE_SMB_CLK

2.5-V

R1

W34

Temperature monitor SMB clock

SENSE_SMB_DATA

2.5-V

R4

AH32

Temperature monitor SMB data

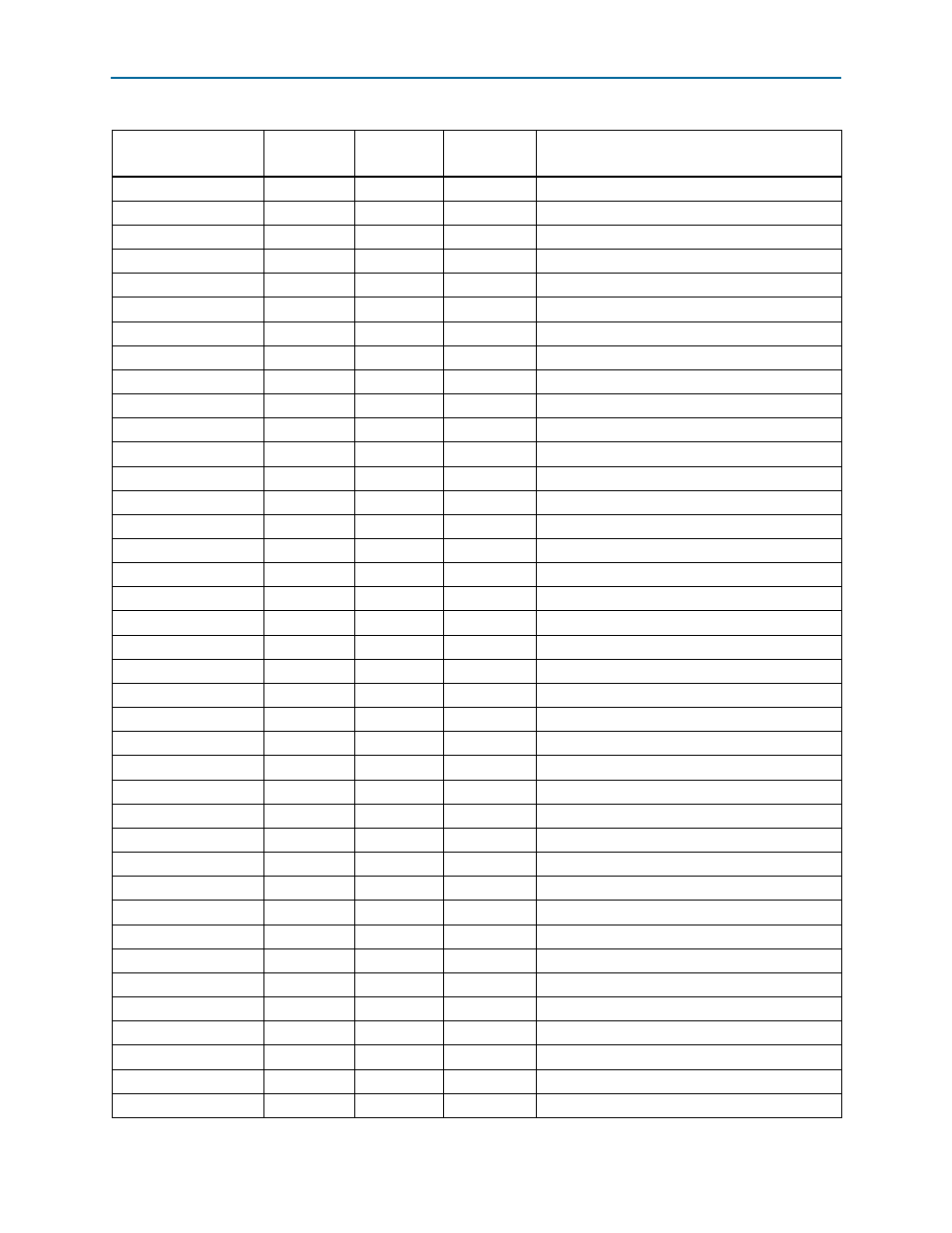

Table 2–6. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 4)

Schematic Signal

Name

I/O Standard

EPM2210

Pin Number

EP4SGX230

Pin Number

Description