Altera Stratix IV GX FPGA Development Board User Manual

Page 68

2–60

Chapter 2: Board Components

Memory

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

November 2010

Altera Corporation

U30.F1

Data bus

FSM_D20

2.5-V

G31

U30.E2

Data bus

FSM_D19

N30

U30.E1

Data bus

FSM_D18

M30

U30.D2

Data bus

FSM_D17

D33

U30.D1

Data bus

FSM_D16

C33

U30.G11

Data bus

FSM_D15

N31

U30.G10

Data bus

FSM_D14

M31

U30.F11

Data bus

FSM_D13

C32

U30.F10

Data bus

FSM_D12

B32

U30.E11

Data bus

FSM_D11

J32

U30.E10

Data bus

FSM_D10

H32

U30.D11

Data bus

FSM_D9

D35

U30.D10

Data bus

FSM_D8

C35

U30.M11

Data bus

FSM_D7

N28

U30.M10

Data bus

FSM_D6

M28

U30.L11

Data bus

FSM_D5

D31

U30.L10

Data bus

FSM_D4

C31

U30.K11

Data bus

FSM_D3

K30

U30.K10

Data bus

FSM_D2

J30

U30.J11

Data bus

FSM_D1

D34

U30.J10

Data bus

FSM_D0

C34

U30.N11

Data bus parity byte lane 0

SRAM_DQP0

F35

U30.C11

Data bus parity byte lane 1

SRAM_DQP1

AJ32

U30.C1

Data bus parity byte lane 2

SRAM_DQP2

N33

U30.N1

Data bus parity byte lane 3

SRAM_DQP3

AJ35

U30.B6

Clock

SRAM_CLK

AE26

U30.B8

Output enable

SRAM_OEn

AK34

U30.A3

Chip enable

SRAM_CEn

AT30

U30.B5

Byte lane 0 write enable

SRAM_BWn0

AH27

U30.A5

Byte lane 1 write enable

SRAM_BWn1

AR31

U30.A4

Byte lane 2 write enable

SRAM_BWn2

AH28

U30.B4

Byte lane 3 write enable

SRAM_BWn3

AL29

U30.A7

Byte write enable

SRAM_BWEn

AK30

U30.B7

Global write enable

SRAM_GWn

AC29

U30.A8

Address status controller

SRAM_ADSCn

AM31

U30.B9

Address status processor

SRAM_ADSPn

AG28

U30.A9

Address valid

SRAM_ADVn

AU32

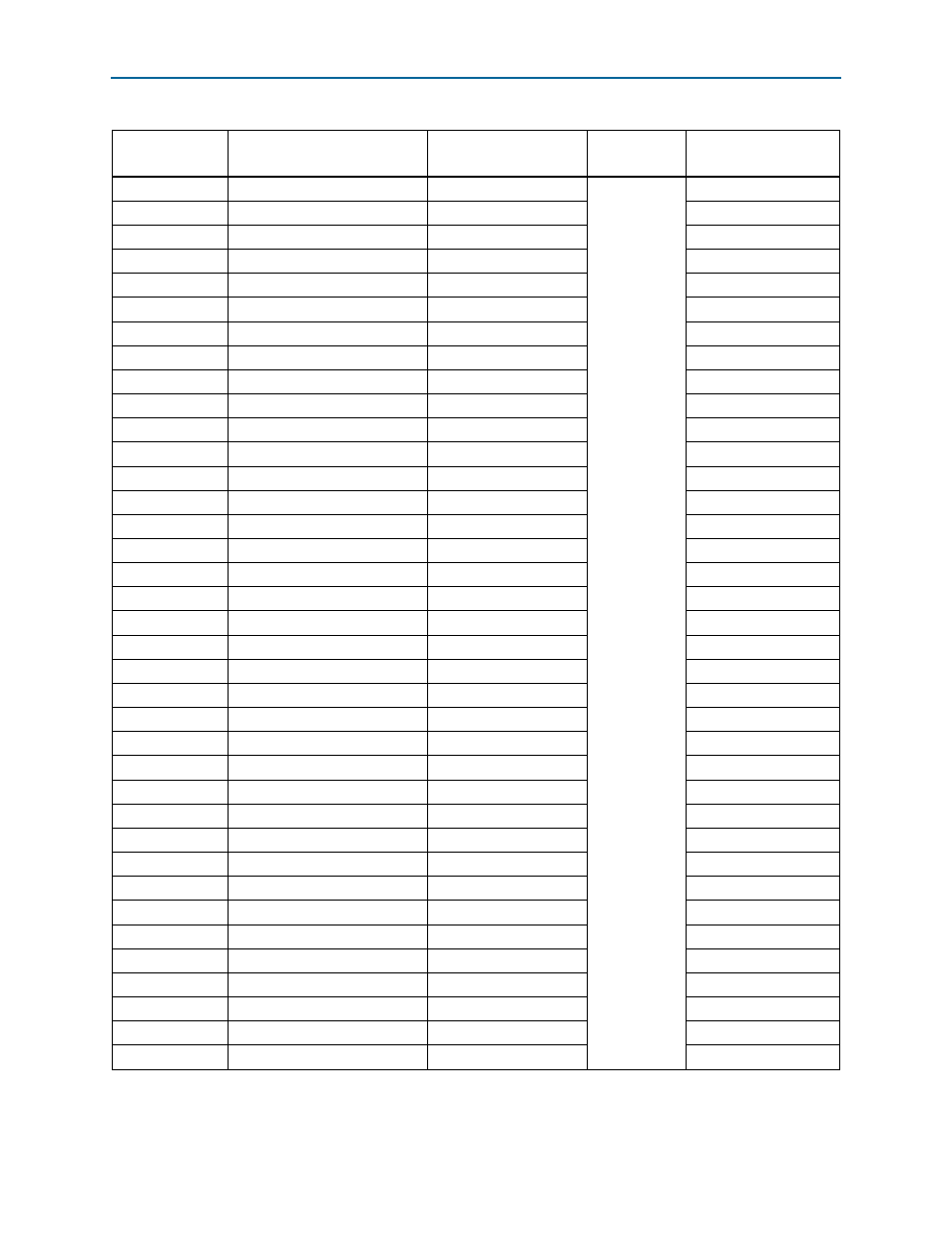

Table 2–54. SSRAM Pin Assignments, Schematic Signal Names, and Functions (Part 2 of 3)

Board Reference

Description

Schematic Signal Name

I/O Standard

Stratix IV GX Device

Pin Number