Qdrii+ top port 1, Qdrii+ top port 1 –56 – Altera Stratix IV GX FPGA Development Board User Manual

Page 64

2–56

Chapter 2: Board Components

Memory

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

November 2010

Altera Corporation

lists the QDRII+ top port 0 component reference and manufacturing

information.

QDRII+ Top Port 1

The QDRII+ top port 1 consists of a single QDRII+ burst-of-4 SRAM, providing

4 Mbyte with an 18-bit read data bus and an 18-bit write data bus.

This memory interface is designed to run between 120 MHz, the minimum frequency

for this device, and 400 MHz for a maximum theoretical bandwidth of over 14.4 Gbps

for reading and 14.4 Gbps for writing. The internal bus in the FPGA is typically 2 or 4

times the width at full rate or half rate respectively. For example, a 400 MHz 18-bit

interface becomes a 200 MHz 72 bit bus.

lists the QDRII+ top port 1

pin assignments, signal names, and functions.

The signal names and types are relative to the Stratix IV GX device in terms of I/O

setting and direction.

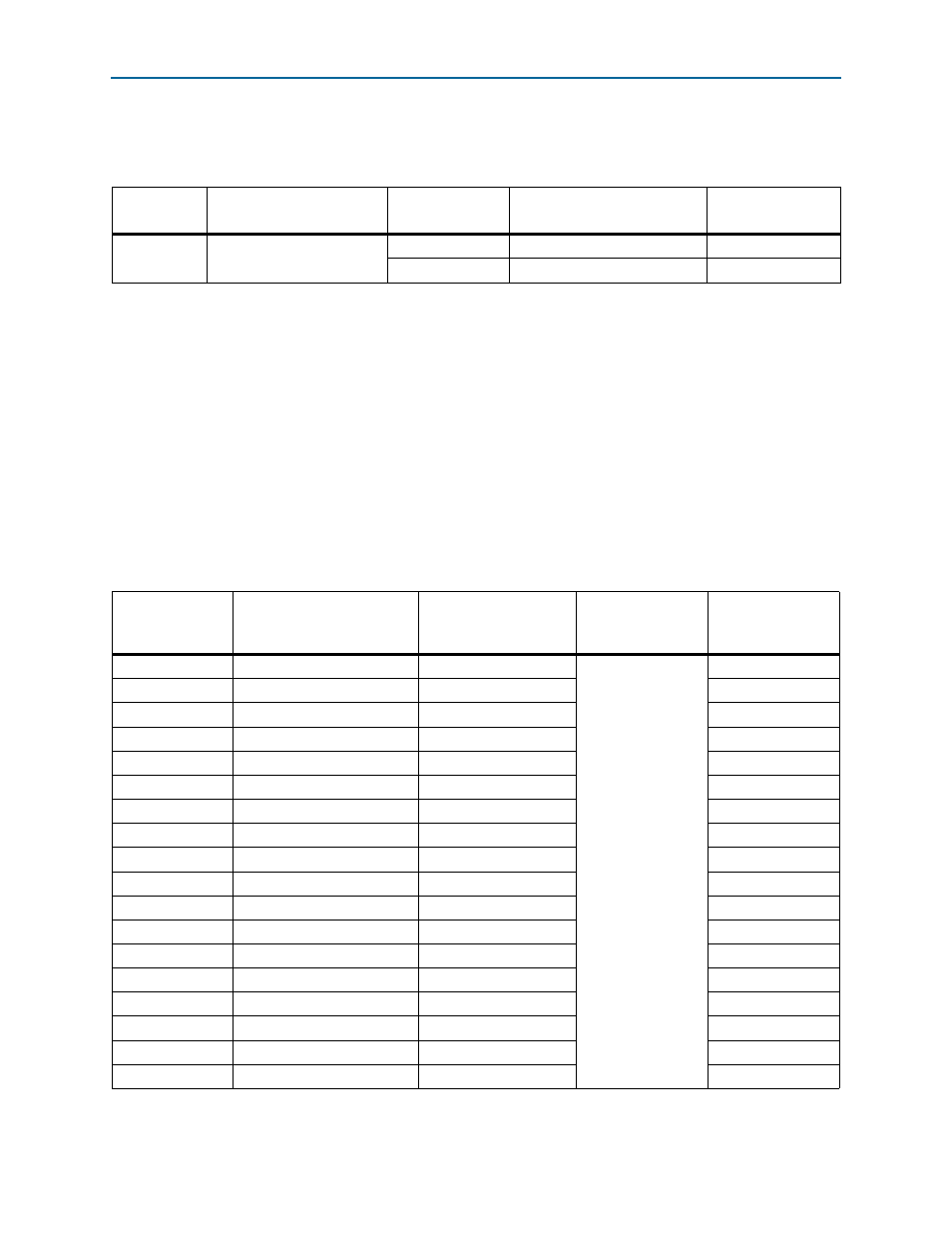

Table 2–51. QDRII+ Top Port 0 Component Reference and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U22

QDRII+, 4 M × 18, 400 MHZ

Cypress

CY7C2563KV18-400BZXC

NEC

uPD44647186AF5-E22-FQ1

Table 2–52. QDRII+ Top Port 1 Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 3)

Board Reference

Description

Schematic Signal Name

I/O Standard

Stratix IV GX

Device

Pin Number

U7.A10

Address bus

QDR2TOP1_A19

1.5-V HSTL Class I

F20

U7.A3

Address bus

QDR2TOP1_A18

B17

U7.A9

Address bus

QDR2TOP1_A17

G20

U7.R7

Address bus

QDR2TOP1_A16

E17

U7.R5

Address bus

QDR2TOP1_A15

J18

U7.R4

Address bus

QDR2TOP1_A14

M19

U7.R3

Address bus

QDR2TOP1_A13

R18

U7.P8

Address bus

QDR2TOP1_A12

F18

U7.P7

Address bus

QDR2TOP1_A11

F17

U7.P5

Address bus

QDR2TOP1_A10

F16

U7.P4

Address bus

QDR2TOP1_A9

P18

U7.N7

Address bus

QDR2TOP1_A8

D17

U7.N6

Address bus

QDR2TOP1_A7

G18

U7.N5

Address bus

QDR2TOP1_A6

L19

U7.C7

Address bus

QDR2TOP1_A5

G19

U7.C5

Address bus

QDR2TOP1_A4

C18

U7.B8

Address bus

QDR2TOP1_A3

A18

U7.B4

Address bus

QDR2TOP1_A2

A17