Altera Stratix IV GX FPGA Development Board User Manual

Page 67

Chapter 2: Board Components

2–59

Memory

November 2010

Altera Corporation

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

lists the SSRAM

pin assignments, signal names, and functions. The signal

names and types are relative to the Stratix IV GX device in terms of I/O setting and

direction.

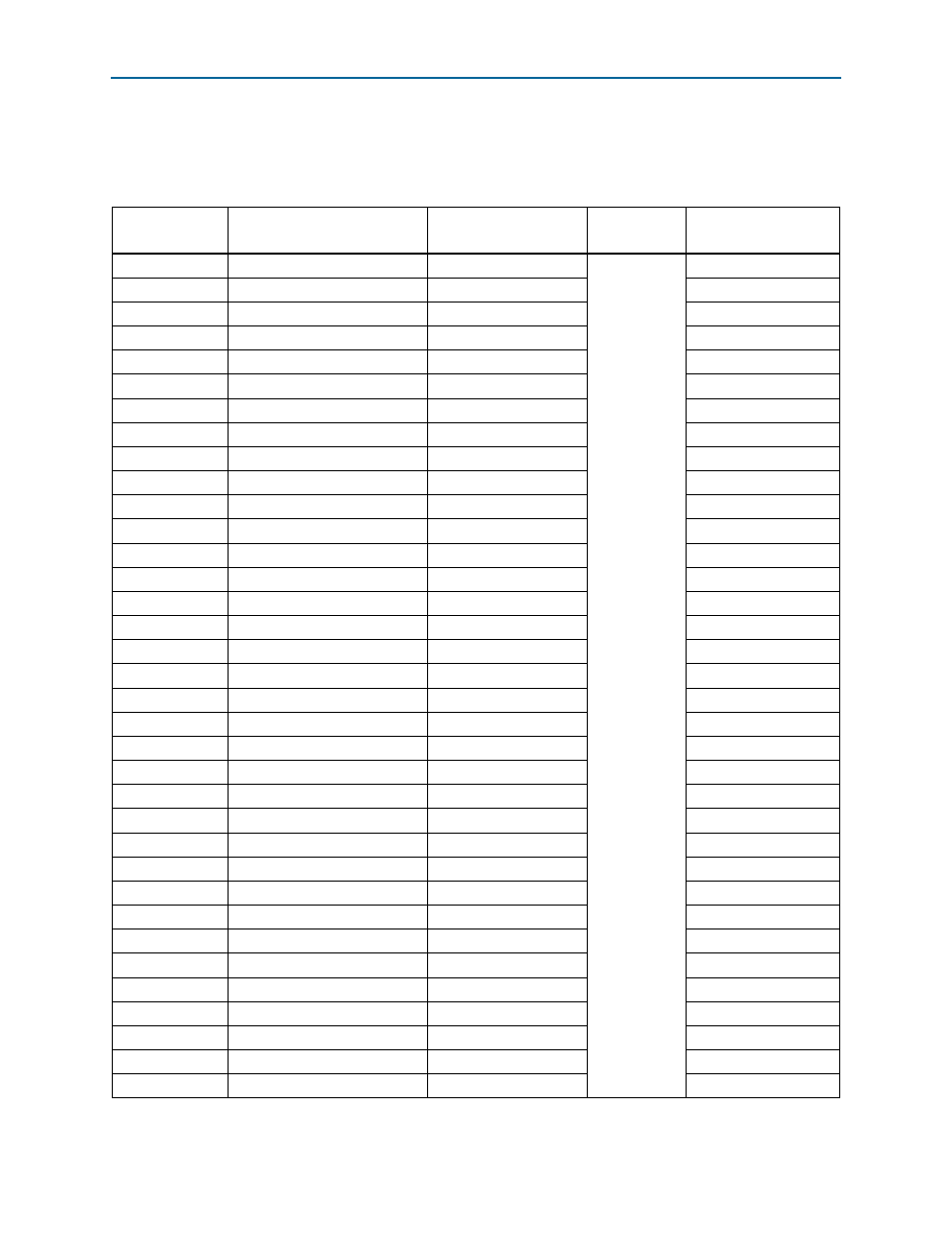

Table 2–54. SSRAM Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 3)

Board Reference

Description

Schematic Signal Name

I/O Standard

Stratix IV GX Device

Pin Number

U30.P2

Address bus (576 M expansion)

FSM_A25

2.5-V

AP30

U30.C10

Address bus (288 M expansion)

FSM_A24

AN30

U30.B11

Address bus (144 M expansion)

FSM_A23

AL31

U30.A1

Address bus (72 M expansion)

FSM_A22

AK31

U30.B1

Address bus (36 M expansion)

FSM_A21

AR32

U30.R11

Address bus

FSM_A20

AP32

U30.R10

Address bus

FSM_A19

AH29

U30.R9

Address bus

FSM_A18

AG29

U30.R8

Address bus

FSM_A17

AR35

U30.R4

Address bus

FSM_A16

AP35

U30.R3

Address bus

FSM_A15

AL32

U30.P11

Address bus

FSM_A14

AK32

U30.P10

Address bus

FSM_A13

AU33

U30.P9

Address bus

FSM_A12

AT33

U30.P8

Address bus

FSM_A11

AH30

U30.P4

Address bus

FSM_A10

AJ31

U30.P3

Address bus

FSM_A9

AR34

U30.N6

Address bus

FSM_A8

AT34

U30.B10

Address bus

FSM_A7

AE27

U30.B2

Address bus

FSM_A6

AD27

U30.A10

Address bus

FSM_A5

AP34

U30.A2

Address bus

FSM_A4

AN33

U30.P6

Address bus

FSM_A3

AD26

U30.R6

Address bus

FSM_A2

AC26

U30.M2

Data bus

FSM_D31

T28

U30.M1

Data bus

FSM_D30

R28

U30.L2

Data bus

FSM_D29

F32

U30.L1

Data bus

FSM_D28

E32

U30.K2

Data bus

FSM_D27

L31

U30.K1

Data bus

FSM_D26

K31

U30.J2

Data bus

FSM_D25

F31

U30.J1

Data bus

FSM_D24

E31

U30.G2

Data bus

FSM_D23

N29

U30.G1

Data bus

FSM_D22

M29

U30.F2

Data bus

FSM_D21

H31