Fpga registers – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

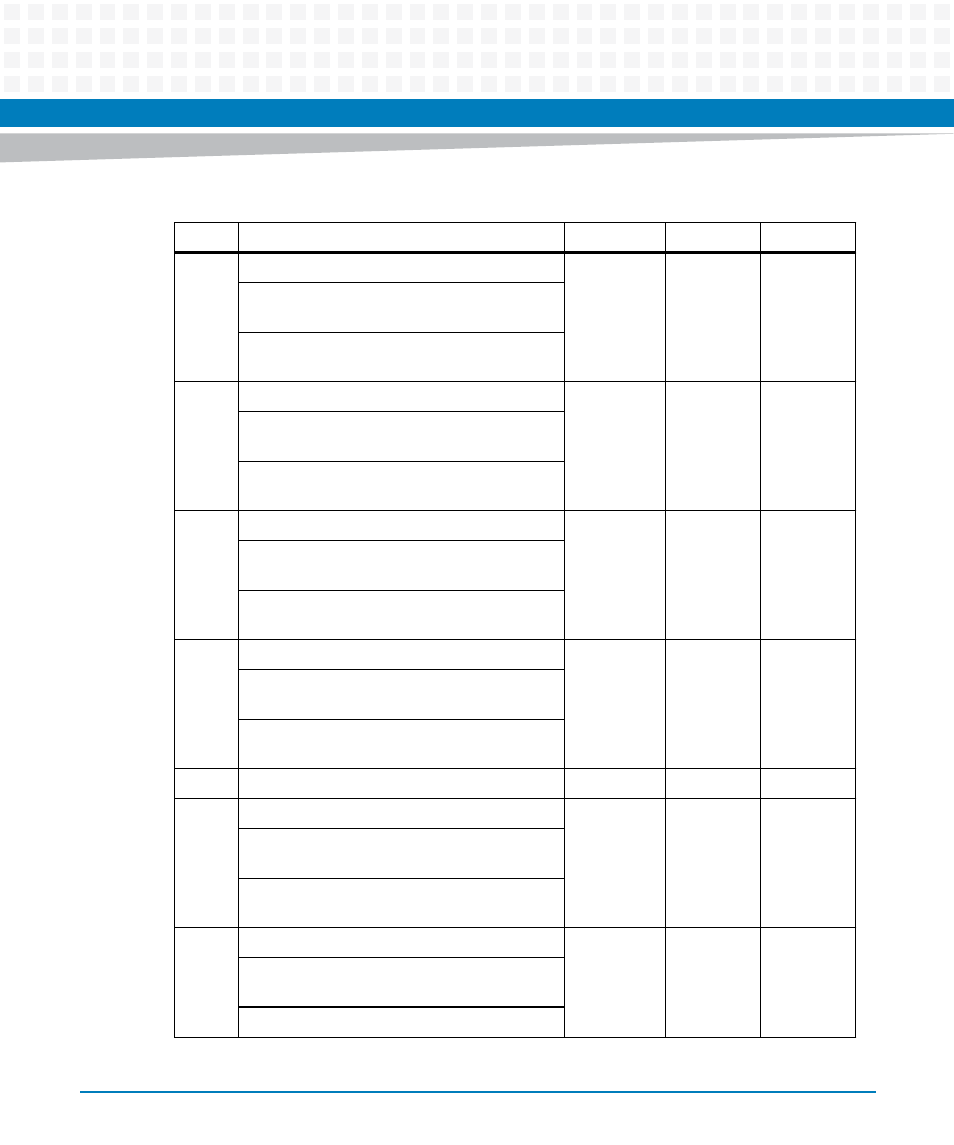

Page 125

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

106

1

FRAM

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected unless protection

is overridden by RTM switch.

2

IPMC User ROM

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected unless protection

is overridden by RTM switch.

3

NAND Flash Controller

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected unless protection

is overridden by RTM switch.

4

PCIE Switch SPI ROM

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected unless protection

is overridden by RTM switch.

5

Reserved

0

RO

RO

6

VPD ROM

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected unless protection

is overridden by RTM switch.

7

XMC

0

R/W

RO

0: Device write is allowed unless protected by

NVMRO.

1: Device is write protected.

Table 7-10 Memory Write Protect Register - 0x0B (continued)

Bit #

Description

Default

LPC Access

I2C Access