15 misc 2 control and status register - 0x11, Table 7-15, Misc 2 control and status register - 0x11 – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 129: Fpga registers

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

110

7.1.15 Misc 2 Control and Status Register - 0x11

3

UART Transceiver Internal Loopback Enable

1

R/W

-

0: Loopback enabled

1: Loopback disabled

4

VPX REFCLK Frequency Select

0

R/W

-

0: 25 MHz.

1: 100MHz

5

Reserved

0

RO

-

6

GDISCRETE1 Power Fail LED Blinking Sync

Enable

0

R/W

-

0: Function disabled.

1: Function enabled.

7

Reserved

0

RO

-

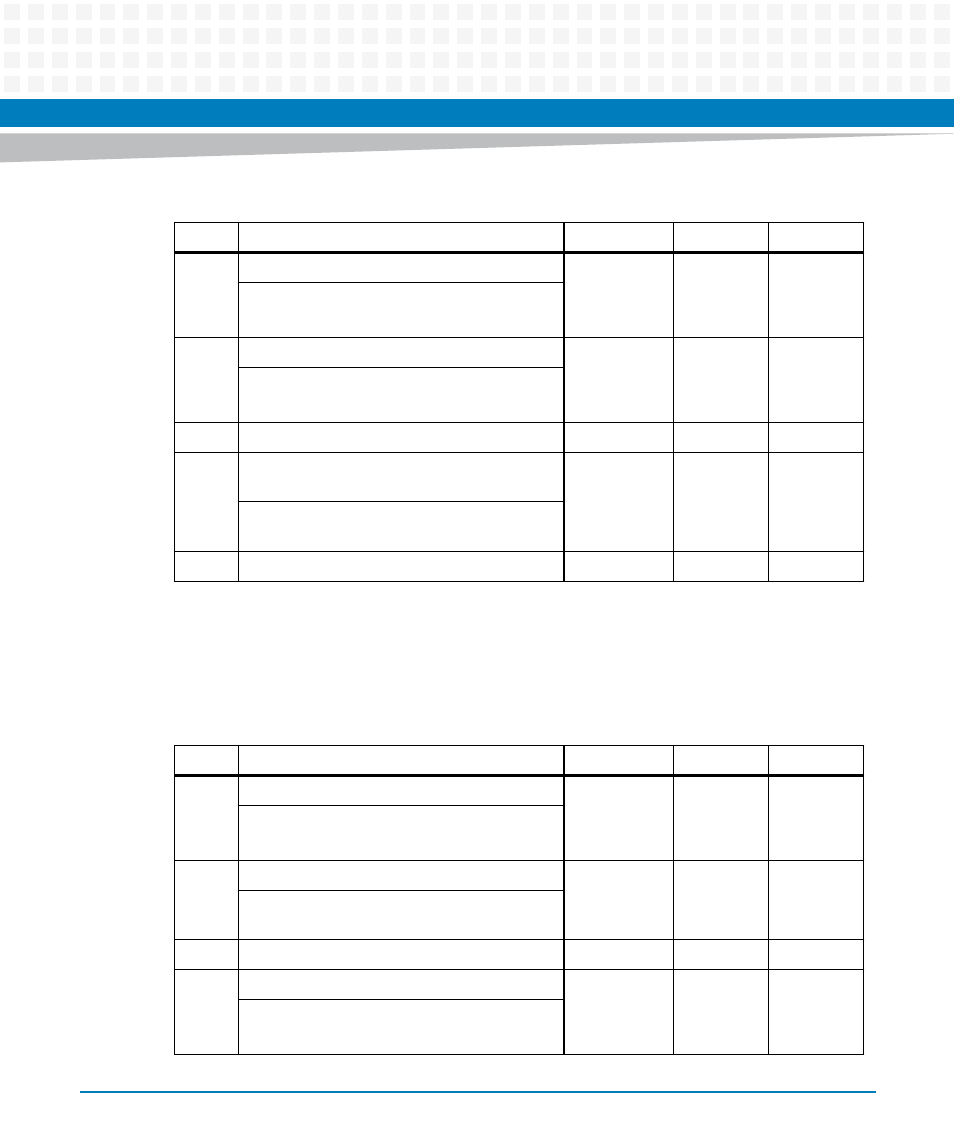

Table 7-14 Misc 1 Control and Status Register - 0x10 (continued)

Bit #

Description

Default

LPC Access

I2C Access

Table 7-15 Misc 2 Control and Status Register - 0x11

Bit #

Description

Default

LPC Access

I2C Access

0

USB Port Power Enable

1

R/W

RO

0: Port power disabled

1: Port power enabled

1

PCH USB OCP# Status

Ext.

RO

RO

0: Over-current indication

1: No Over-current indication

2

Reserved

0

RO

RO

3

IPMC Watchdog NMI

0

R/W1TC

RO

0: NMI not due to IPMC watchdog reset

1: NMI due to IPMC watchdog reset