16 dip switch status register - 0x14, Table 7-16, Dip switch status register - 0x14 – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 130: Fpga registers

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

111

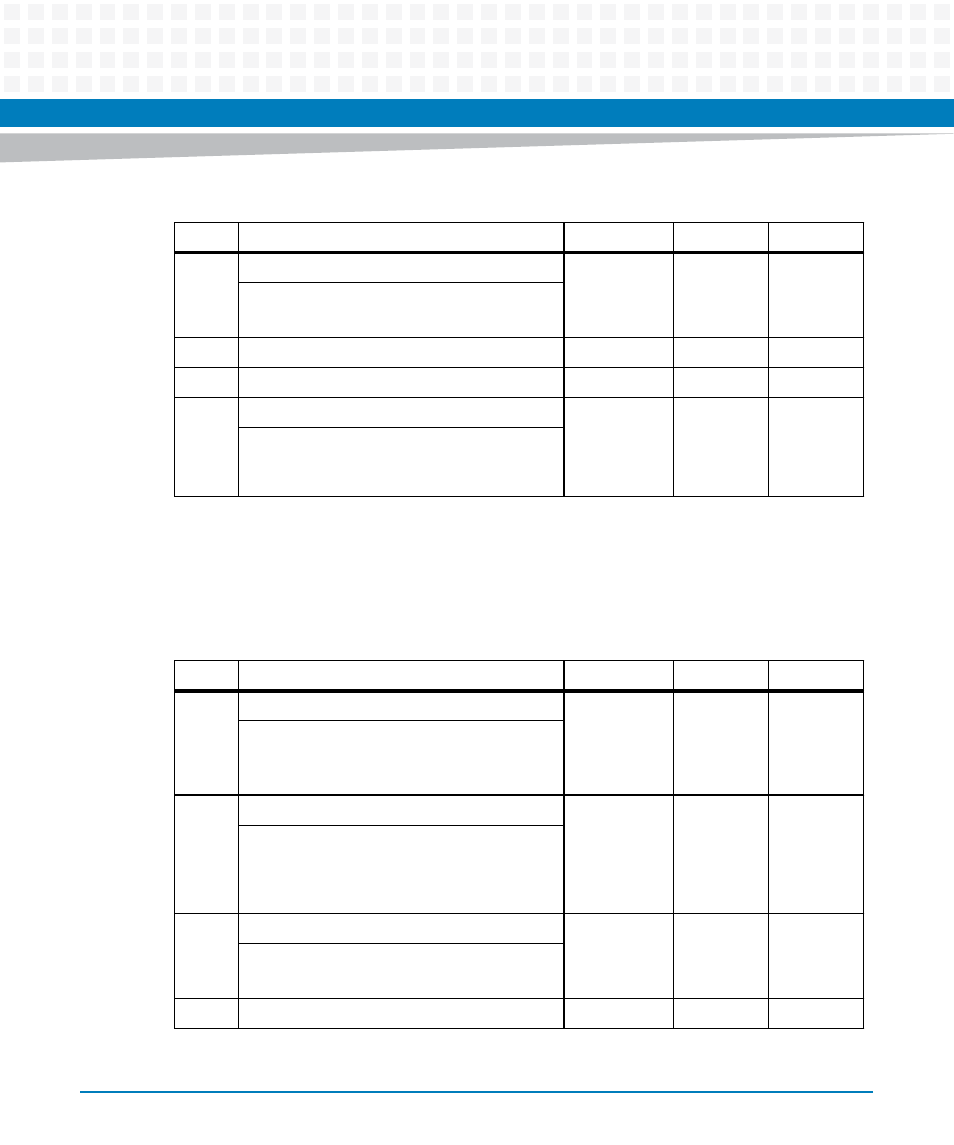

7.1.16 DIP Switch Status Register - 0x14

4

IPMC NMI

0

R/W1TC

RO

0: NMI not due to IPMC NMI

1: NMI due to IPMC NMI

5

IPMC GP Signal (Reserved for future)

Ext.

RO

RO

6

Reserved

0

RO

RO

7

User LED Enable

1

R/W

RO

0: User, power fail and POST Code LEDs off.

1: Normal functions of user, power fail and

POST Code LEDs On.

Table 7-15 Misc 2 Control and Status Register - 0x11 (continued)

Bit #

Description

Default

LPC Access

I2C Access

Table 7-16 DIP Switch Status Register - 0x14

Bit #

Description

Default

LPC Access

I2C Access

0

Standalone Mode

Ext.

RO

-

0: Board is in standalone mode, IPMI is

disabled

1: IPMI is enabled

1

TBSWAP (Boot Bank Switch)

Ext

RO

-

0: Board will boot from Flash 1 (bank B) upon

power on if IPMC is not present (bit 0 is zero)

1: Board will boot from Flash 0 (bank A) upon

power on if IPMC is not present (bit 0 is zero)

2

Load Default BIOS

Ext.

RO

-

0: Load BIOS defaults

1: Use saved BIOS settings

7:3

Reserved

0

RO

-