14 misc 1 control and status register - 0x10, Table 7-14, Misc 1 control and status register - 0x10 – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 128: Fpga registers

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

109

7.1.14 Misc 1 Control and Status Register - 0x10

4

PCH S4 Sleep Indication

Ext.

RO

-

0: SLP_S4# Sleep signal asserted.

1: SLP_S4# Sleep signal de-asserted.

5

PCH S3 Sleep Indication.

Ext.

RO

-

0: SLP_S3# sleep signal asserted.

1: SLP_S3# sleep signal de-asserted.

6

PCH Suspend Well Sleep Indication

Ext.

RO

-

0: SLP_SUS# sleep signal asserted.

1: SLP_SUS# sleep signal de-asserted.

7

PCH Active Sleep Well Sleep Indication

Ext.

RO

-

0: SLP_A# sleep signal asserted.

1: SLP_A# sleep signal de-asserted.

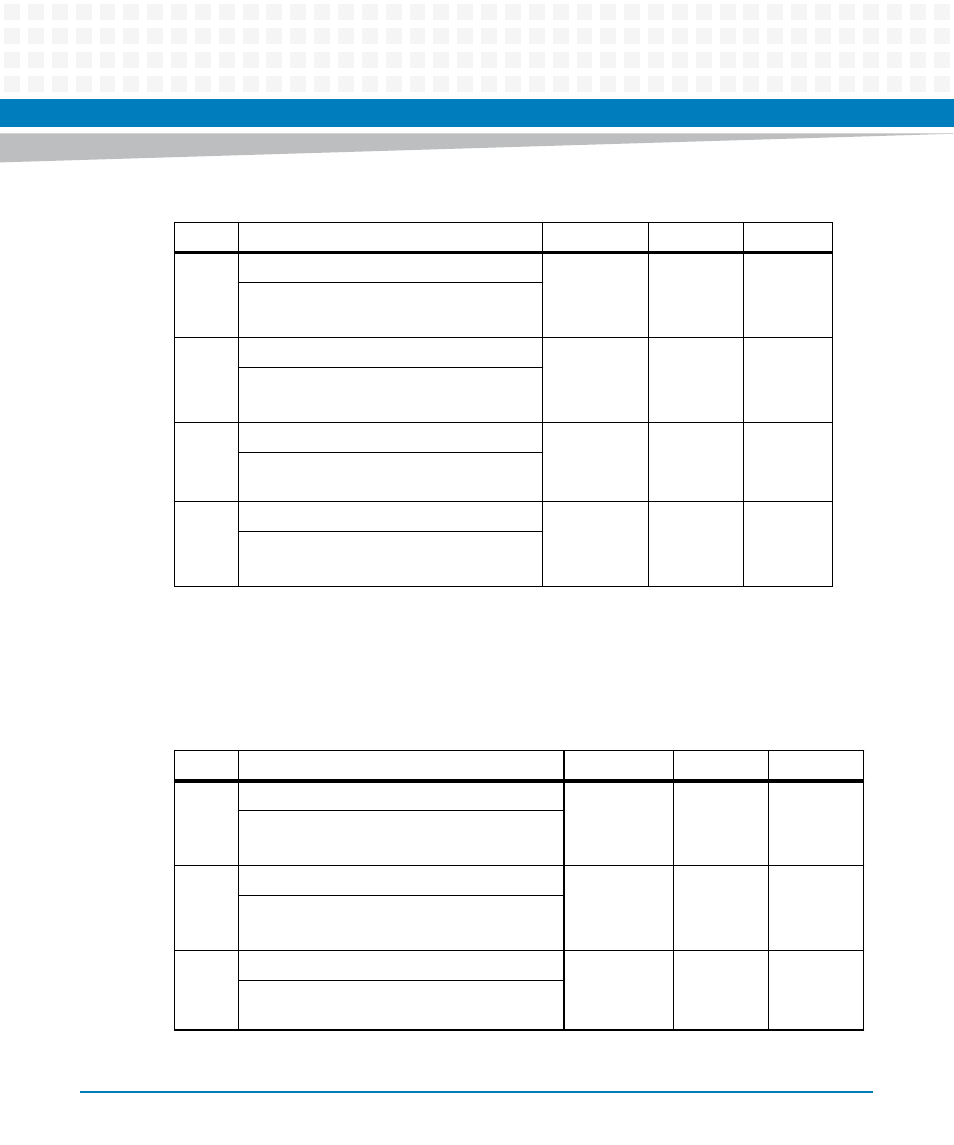

Table 7-13 System Status Register - 0x0E (continued)

Bit #

Description

Default

LPC Access

I2C Access

Table 7-14 Misc 1 Control and Status Register - 0x10

Bit #

Description

Default

LPC Access

I2C Access

0

COM0 UART RS232/RS485 Mode Select

0

R/W

-

0: RS232 interface mode selected

1: RS485/422 interface mode selected

1

COM1 UART RS232/RS485 Mode Select

0

R/W

-

0: RS232 interface mode selected

1: RS485/422 interface mode selected

2

UART Transceiver Enable

1

R/W

-

0: Transceiver disabled

1: Transceiver enabled