26 vpx system register - 0x24, Table 7-26, Vpx system register - 0x24 – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 138: Fpga registers

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

119

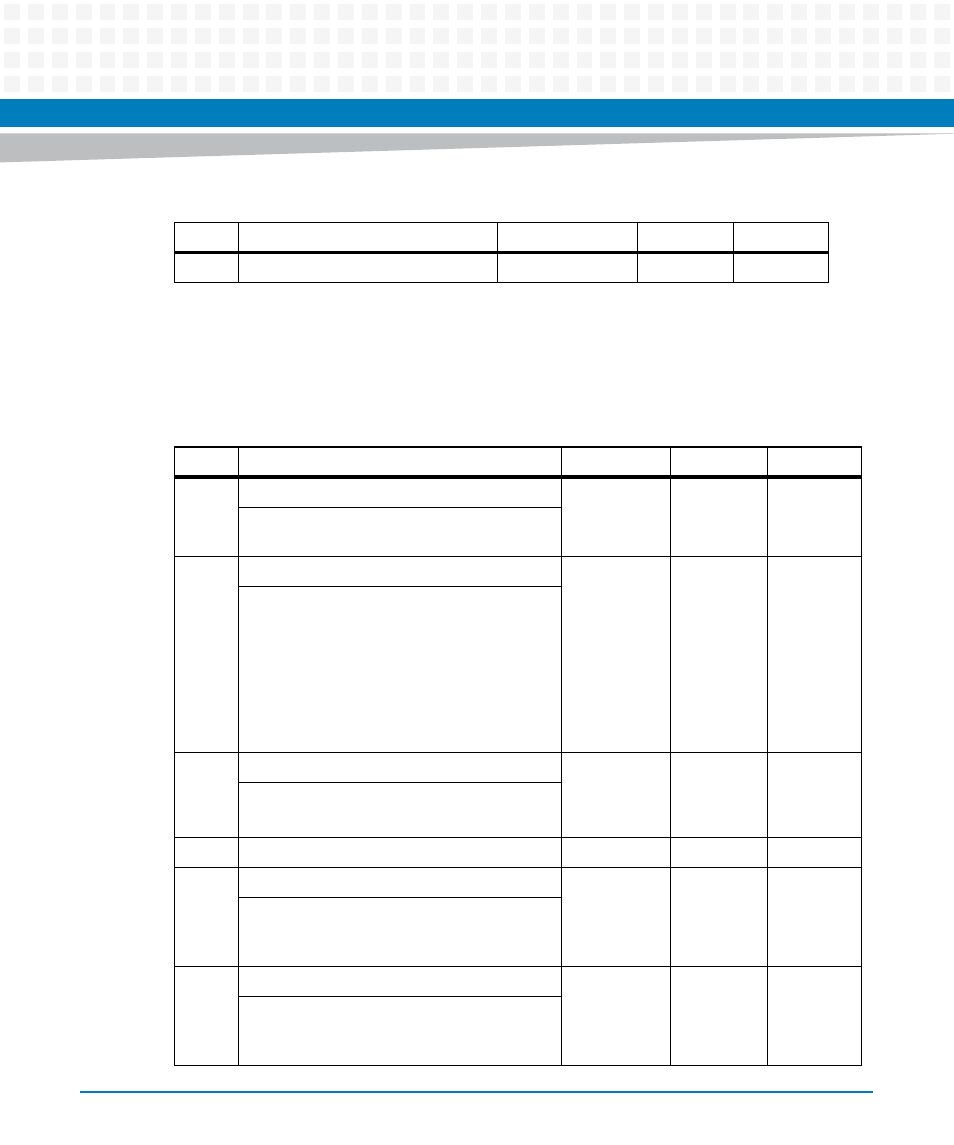

7.1.26 VPX System Register - 0x24

7:3

Reserved

0x0

RO

-

Table 7-25 FRAM Page Access Register - 0x20 (continued)

Bit #

Description

Default

LPC Access

I2C Access

Table 7-26 VPX System Register - 0x24

Bit #

Description

Default

LPC Access

I2C Access

0

MRST# Mask

0

R/W

RO

0: MRST# input is not masked

1: MRST# input is masked

1

NVMRO

Ext.

RO

RO

0: NVMRO is cleared by backplane/other

boards to logic zero. It will allow all

programmable parts on the board to be read

or written.

1: NVMRO is set by backplane to logic one. It

will allow all programmable parts on the

board to be read, but may prohibit write

depending upon override switch settings.

2

System Slot

Ext.

RO

RO

0: Board is installed in system slot

1: Board is installed in non-system slot

5:3

Reserved

0x0

RO

RO

6

MRST (Masked Reset) to Backplane

0

WO

RO

0: Masked reset is de-asserted to the

backplane

1: Masked reset is generated to the backplane

7

SYS_RST (System Reset) to Backplane

0

WO

RO

0: System reset is de-asserted to the

backplane

1: System reset is generated to the backplane