Avago Technologies LSI53C825AE User Manual

Page 263

Advertising

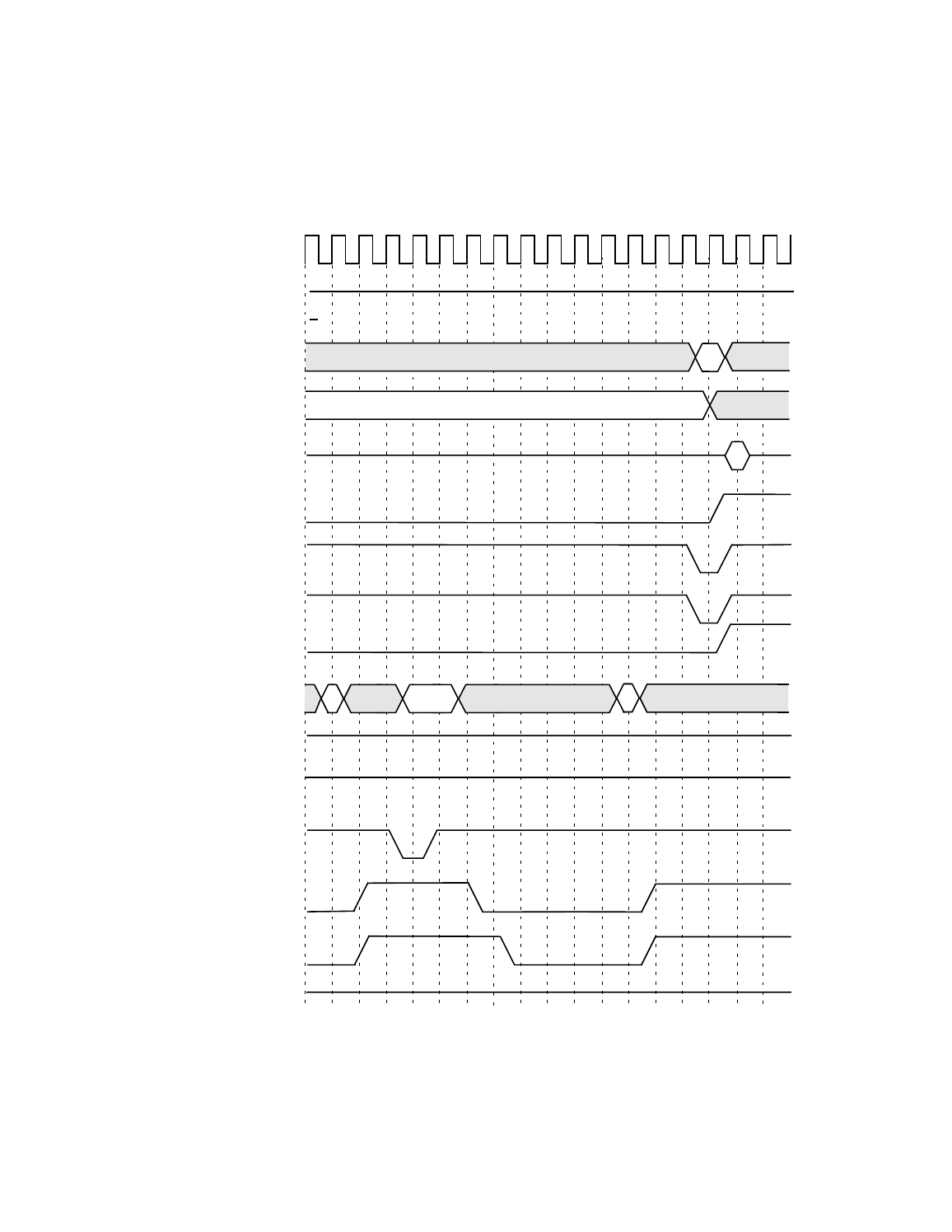

PCI and External Memory Interface Timing Diagrams

6-35

Figure 6.23

Read Cycle, Normal/Fast Memory (

≥

64 Kbytes), Multiple Byte Access (Cont.)

MAD

(Addr Driven by LSI53C825A;

MAS1/

(Driven by LSI53C825A)

MAS0/

(Driven by LSI53C825A)

MCE/

(Driven by LSI53C825A)

MOE/

(Driven by LSI53C825A)

MWE/

(Driven by LSI53C825A)

Data driven by Memory)

CLK

(Driven by System)

PAR

(Driven by LSI53C825A-

IRDY/

(Driven by Master)

TRDY/

(Driven by LSI53C825A)

STOP/

(Driven by LSI53C825A)

DEVSEL/

(Driven by LSI53C825A)

AD

(Driven by LSI53C825A-

C_BE/

(Driven by Master)

FRAME/

(Driven by Master)

Master-Addr; Data)

Master-Addr; Data)

GPIO2_MAS2/

(Driven by LSI53C825A)

Byte Enable

Data In

Lower

Address

Data In

16

18

19

22

24

26

28

30

17

33

20

21

23

25

27

29

31

32

Data

Out

Out

Advertising