Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 31

Altera Corporation

3–5

HardCopy II Clock Uncertainty Calculator User Guide

Design Case Exceptions

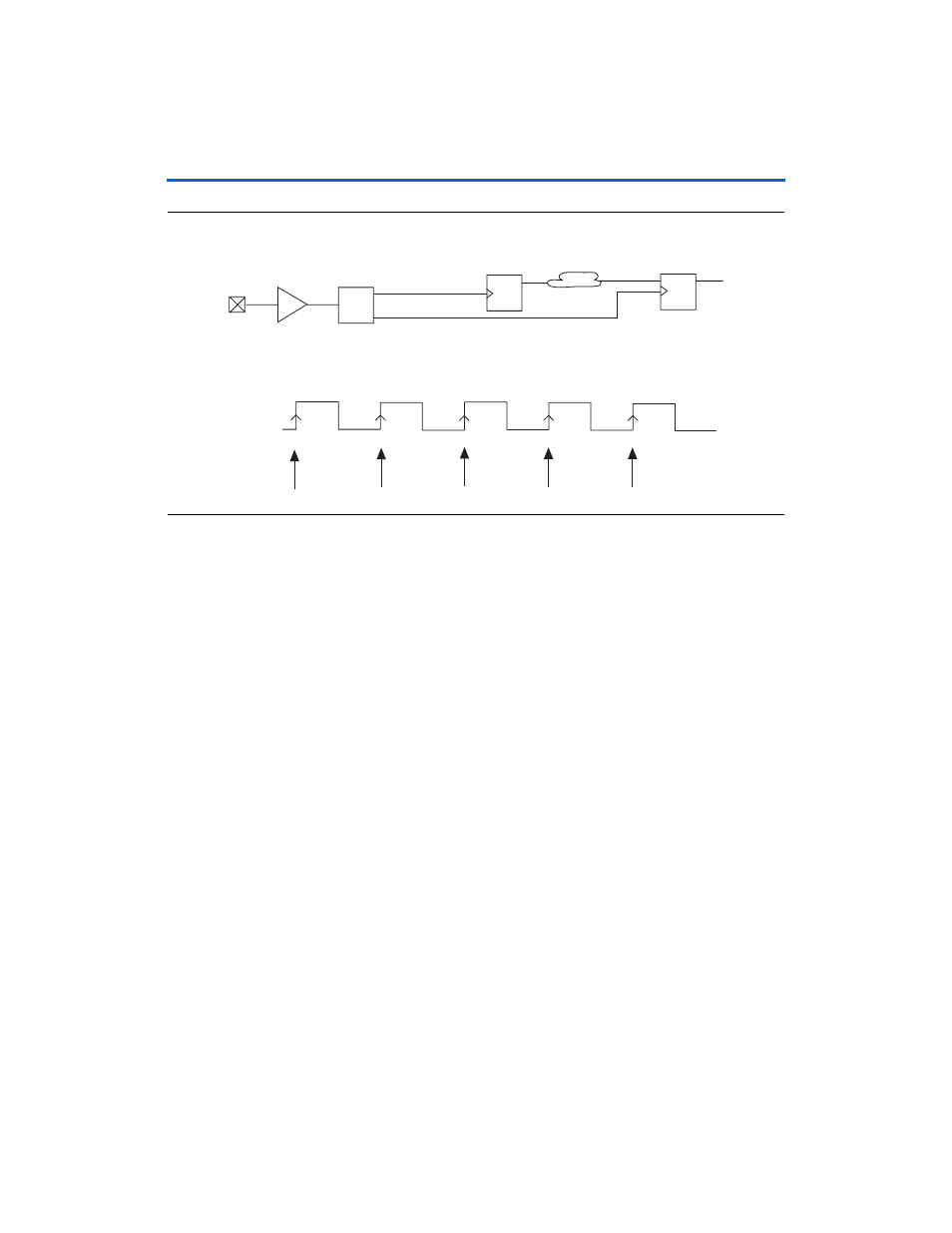

Figure 3–7. Multi-Cycle Clock

In the example shown in

, the multi-cycle path timing

exception is set and the hold margin is not checked at the launch clock

edge, in other words, the hold margin is checked at E1, E2, or E3 edge.

You should use the setup clock uncertainty value from clock uncertainty

calculator for hold clock uncertainty constraints.

shows the clock uncertainty result from the schematic circuit.

The setup clock uncertainty is 100 ps, and the hold clock uncertainty is

50 ps. If the hold margin is on E1, E2, or E3, use the following example:

set_clock_uncertainty -from CLK1 -to CLK2 -hold 100ps

If the hold margin is on E0, use the following example:

set_clock_uncertainty -from CLK1 -to CLK2 -hold 50ps

PLL

INBUF

CLK1

CLK2

E0

E1

E2

E3

E4

Launch

Edge

Setup Check

Possible Hold Checks

Capture

Edge

R1

Source

Register

R2

t

Δ

Destination

Register