I/o interface with pll – Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 43

Advertising

Altera Corporation

A–11

HardCopy II Clock Uncertainty Calculator User Guide

I/O Interface

with PLL

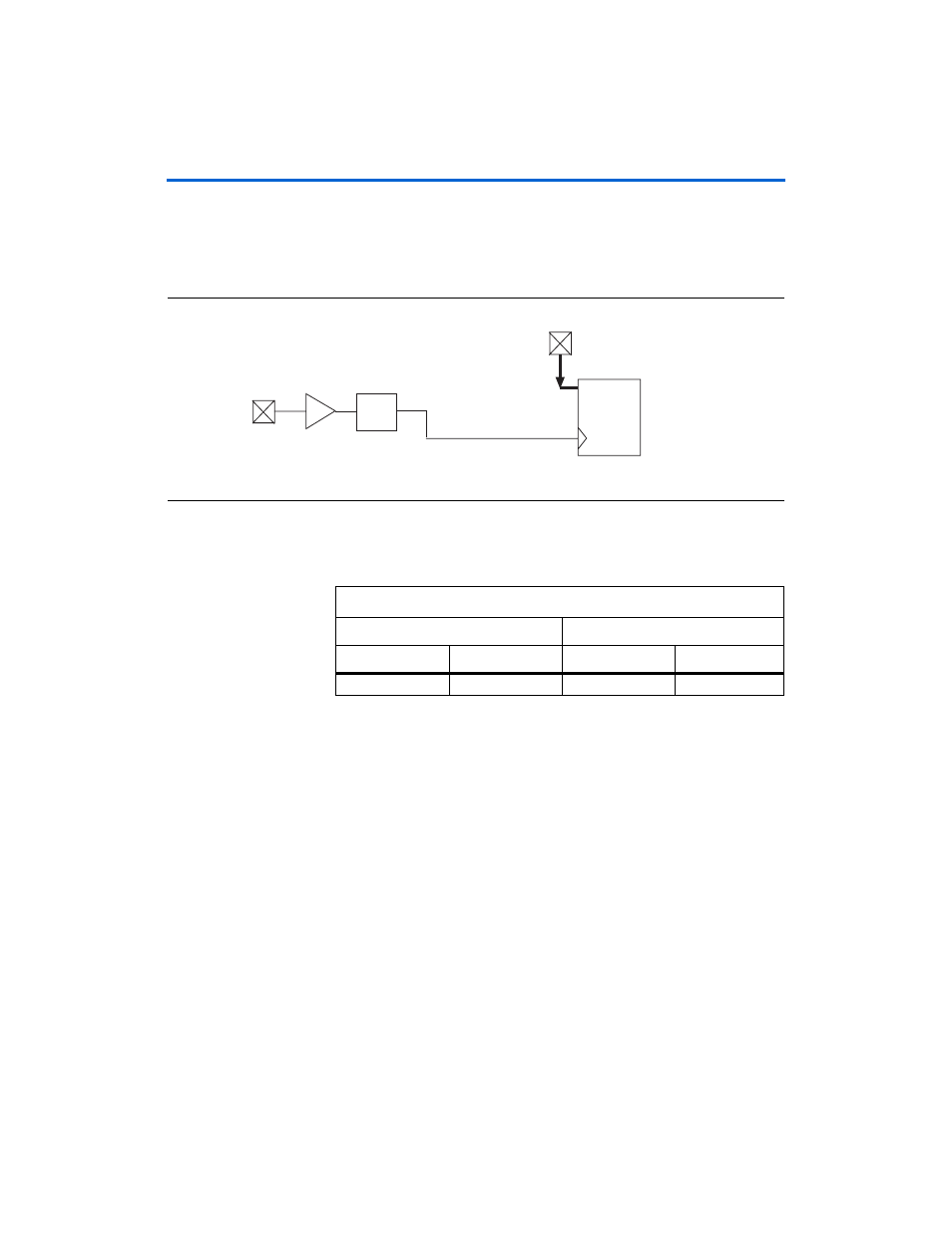

This section provides clock transfer examples for an I/O interface with at

least one PLL.

shows an example of a clock-pair = Off-chip to CLK5

Figure A–11. Input Interface with a PLL

shows input of the PLL index for

, with respect to

the source and destination clocks.

INBUF

CLK5

PLL10

Destination

Register

DATA

Destination

Clock

Table A–11. Location of Input PLLs

Source Clock

Destination Clock

1st PLL

2nd PLL

1st PLL

2nd PLL

0

—

10

—

Advertising