General description, General description –2 – Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 8

1–2

Altera

Corporation

HardCopy II Clock Uncertainty Calculator User Guide

August 2007

General Description

General

Description

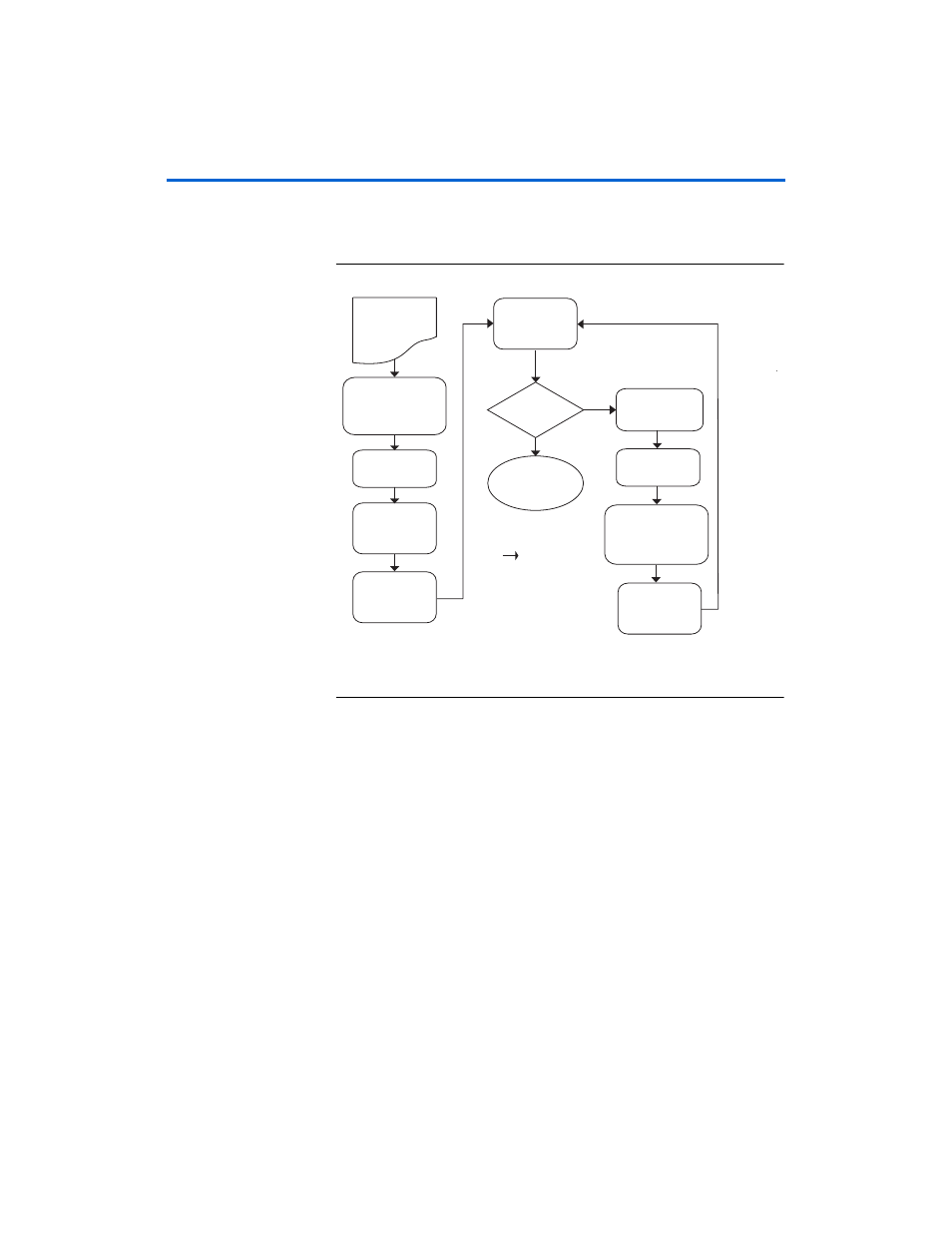

shows the HardCopy II development flow, including the

HardCopy II Clock Uncertainty Calculator flow.

Figure 1–1. Top-level Flow for HardCopy II Development Flow

Note to

(1)

Initially, run clock uncertainty calculator flow on FPGA database; all subsequent

times are found in the HardCopy II database.

f

Refer to the Quartus II Support of HardCopy Series Device chapter in the

Quartus II Handbook for more details.

After the Stratix

®

II FPGA design is compiled and the database is

generated successfully, Altera

®

recommends that you run the clock

uncertainty (CU) calculator flow. Although the Stratix II FPGA database

may not be migrated to a HardCopy II companion device, the source used

to calculate the clock uncertainty in Stratix II devices is same source used

in the initial stage of HardCopy’s clock uncertainty calculation. In

addition, creating and applying the clock uncertainty constraints during

the HardCopy II compilation and static timing analysis will increase

efficiency.

FPGA

Quartus II

Database

Run Clock

Uncertainty

Calculator Flow (1)

(based on FPGA database)

Generate CU

Constraint File

Create HC II

Companion

Revision

Compile for

HardCopy II

TimeQuest

Timing Analyzer

Analysis

Pass?

Done

Fix Timing

Violations

Recompile for

HardCopy II

Generate

Revised CU

Constraint File

Re-run Clock

Uncertainty

Calculator Flow (1)

(based on FPGA database)

No

Yes

Yes

TQ

TimeQuest