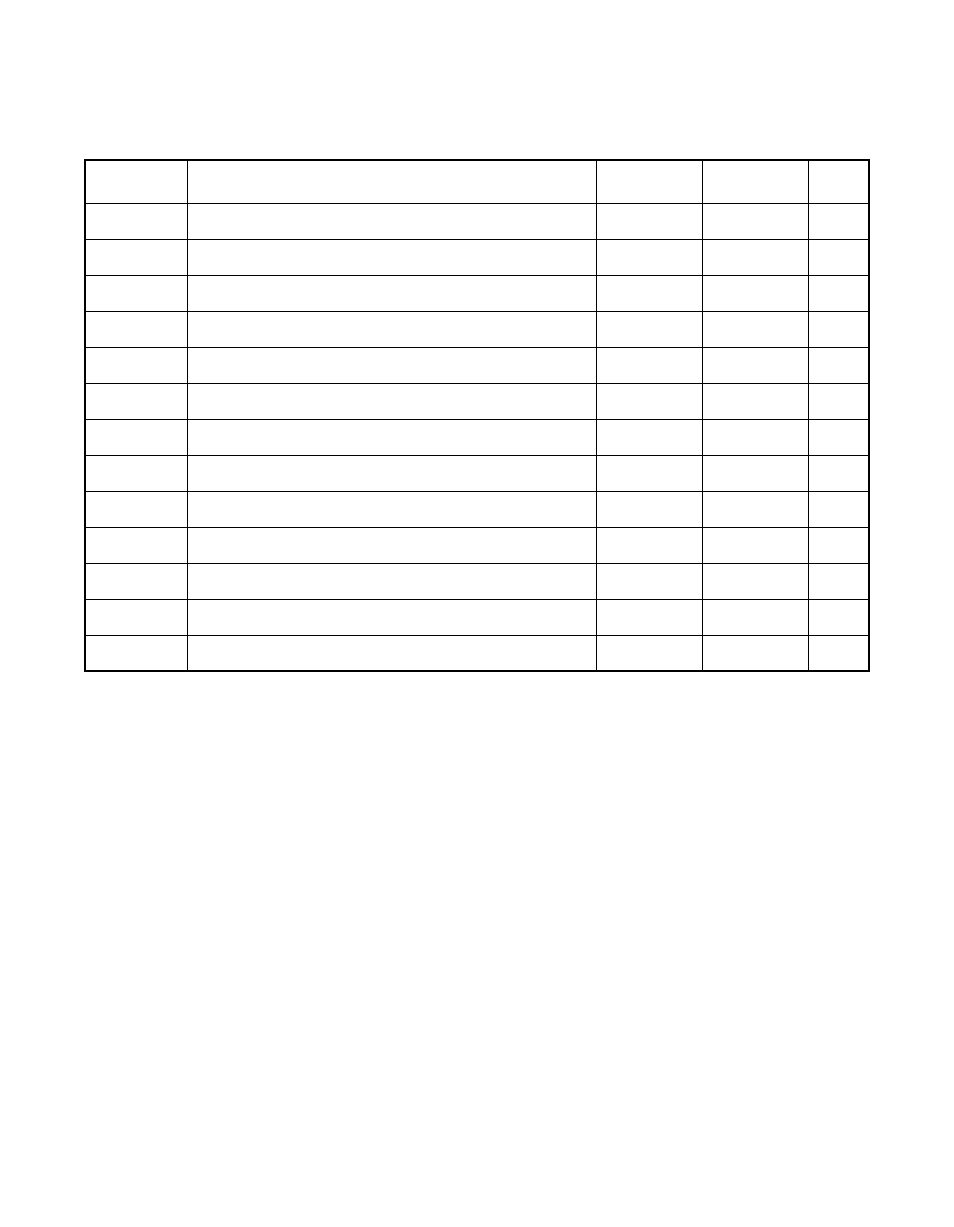

Table 6.29 target read (from external memory), Target read (from external memory) – Avago Technologies LSI53C876E User Manual

Page 253

Advertising

AC Characteristics

6-21

Table 6.29

Target Read (From External Memory)

Symbol

Parameter

1

1. See note on page 6-16 regarding 3.3 V PCI Timing Changes.

Min

Max

Unit

t

1

Shared signal input setup time

7

–

ns

t

2

Shared signal input hold time

0

–

ns

t

3

CLK to shared signal output valid

–

11

ns

t

4

Side signal input setup time

10

–

ns

t

11

Address setup to MAS/ high

25

–

ns

t

12

Address hold from MAS/ high

15

–

ns

t

13

MAS/ pulse width

25

–

ns

t

14

MCE/ low to data clocked in

160

–

ns

t

15

Address valid to data clocked in

205

–

ns

t

16

MOE/ low to data clocked in

100

–

ns

t

17

Data hold from address, MOE/, MCE/ change

0

–

ns

t

18

Address out from MOE/, MCE/ high

50

–

ns

t

19

Data setup to CLK high

5

–

ns

Advertising