1 interrupt acknowledge command, 2 special cycle command, 3 i/o read command – Avago Technologies LSI53C876E User Manual

Page 27: 4 i/o write command, 5 reserved command

PCI Functional Description

2-5

2.1.2.1 Interrupt Acknowledge Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

2.1.2.2 Special Cycle Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

2.1.2.3 I/O Read Command

The I/O Read command reads data from an agent mapped in I/O

address space. All 32 address bits are decoded.

2.1.2.4 I/O Write Command

The I/O Write command writes data to an agent mapped in I/O address

space. All 32 address bits are decoded.

2.1.2.5 Reserved Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

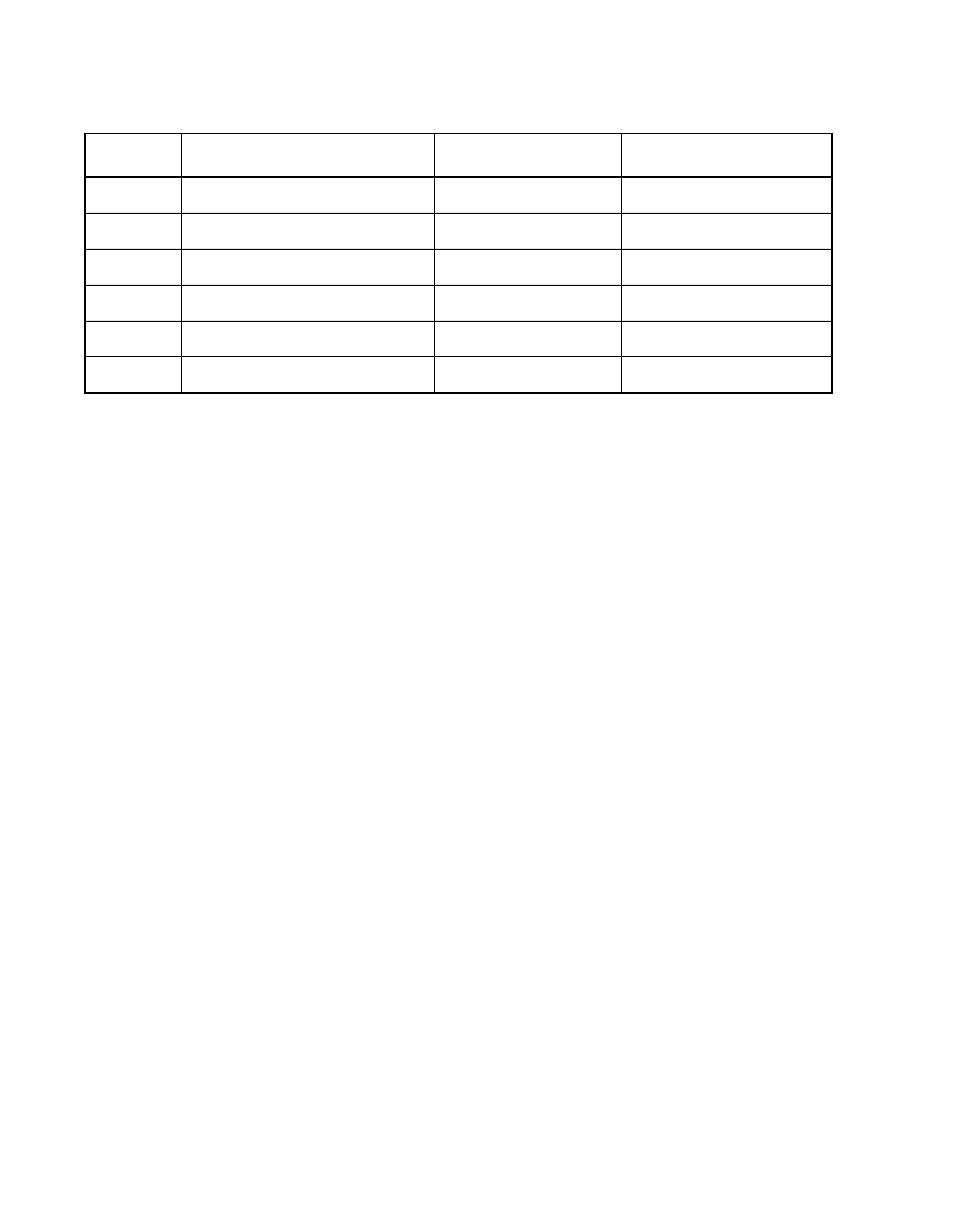

0b1010

Configuration Read

No

Yes

0b1011

Configuration Write

No

Yes

0b1100

Memory Read Multiple

Yes

1

No (defaults to 0110)

0b1101

Dual Address Cycle (DAC)

No

No

0b1110

Memory Read Line

Yes

1

No (defaults to 0110)

0b1111

Memory Write and Invalidate

Yes

2

No (defaults to 0111)

1. See the

register.

2. See the

register.

Table 2.1

PCI Bus Commands and Encoding Types (Cont.)

C_BE[3:0] Command Type

Supported as Master Supported as Slave