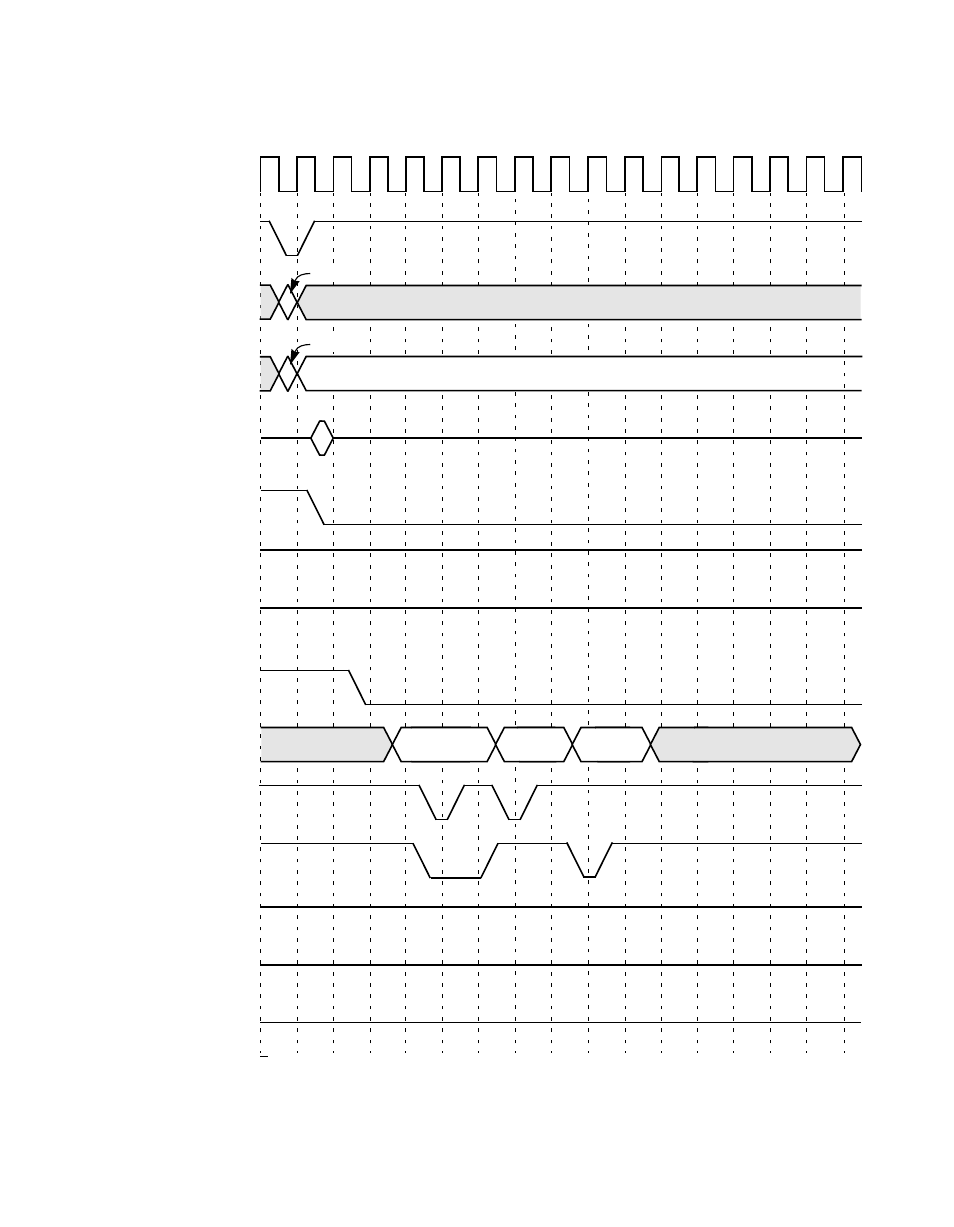

Read cycle, normal/fast memory, 128 kbyte), multiple byte, Access – Avago Technologies LSI53C876E User Manual

Page 278

Advertising

6-46

Electrical Characteristics

Figure 6.23 Read Cycle, Normal/Fast Memory (

≥

128 Kbyte), Multiple Byte Access

CLK

(Driven by System)

FRAME/

(Driven by Master)

AD/

(Driven by Master-Addr;

C_BE/

(Driven by Master)

IRDY/

(Driven by Master)

TRDY/

(Driven by LSI53C876)

STOP/

(Driven by LSI53C876)

(Driven by LSI53C876)

DEVSEL/

LSI53C876-Data)

PAR/

(Driven by Master-Addr;

LSI53C876-Data)

MAD/

(Addr driven by LSI53C876;

(Driven by LSI53C876)

MAS1/

(Driven by LSI53C876)

MAS0/

(Driven by LSI53C876)

MCE/

(Driven by LSI53C876)

MWE/

(Driven by LSI53C876)

MOE/

Addr In

High Order

Address

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Byte Enable

CMD

Middle Order

Address

Low Order

Address

16

In

Data driven by Memory)

Advertising