Altera Nios Development Board User Manual

Page 10

1–2

Altera

Corporation

Nios Development Board Reference Manual, Stratix II Edition

July 2005

General Description

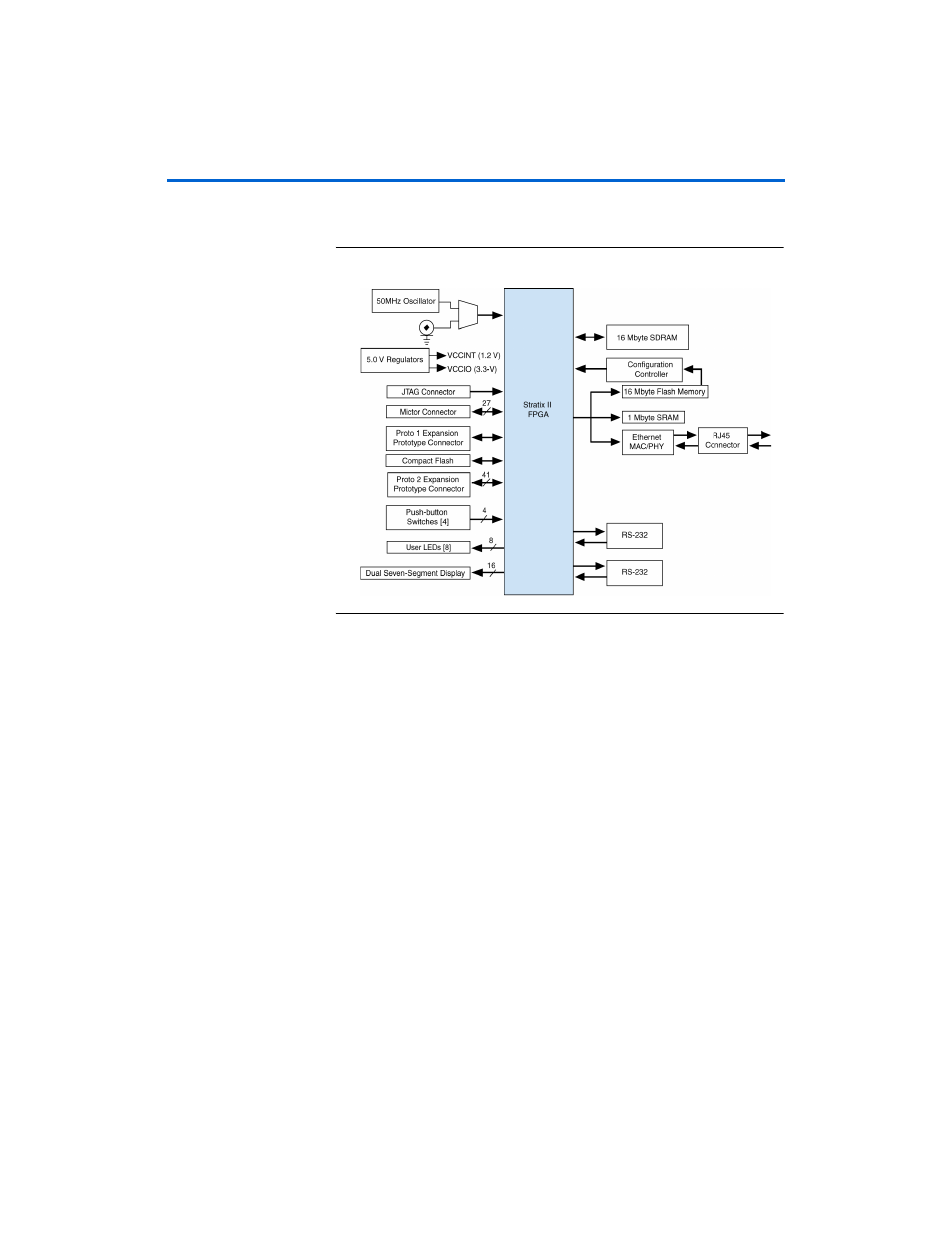

shows a block diagram of the Nios development board.

Figure 1–1. Nios Development Board, Stratix II Edition Block Diagram

1

Early shipments of the Nios development board, Stratix II

edition use an EP2S60F672C5ES device. This is a fully tested

engineering sample (ES) device. However, it has a known issue

affecting the M-RAM blocks. The issue can be worked around

easily, but some consideration is required when migrating

designs based on this device to a non-ES device. There is a label

near the FPGA; if the letters “ES” appear on the label, the device

is an engineering sample.

f

For details, refer to the Stratix II FPGA Family Errata Sheet and the

documented example designs included in the Nios II Development Kit.