Sdram memory (u57) – Altera Nios Development Board User Manual

Page 20

2–12

Altera

Corporation

Nios Development Board Reference Manual, Stratix II Edition

July 2005

SDRAM Memory (U57)

SDRAM Memory

(U57)

The SDRAM device (U57) is a Micron MT48LC4M32B2 with PC100

functionality and self refresh mode. The SDRAM is fully synchronous

with all signals registered on the positive edge of the system clock.

The SDRAM device pins are connected to the Stratix II device (see

). An SDRAM controller peripheral is included with the Nios II

development kit, allowing a Nios II processor to view the SDRAM device

as a large, linearly-addressable memory.

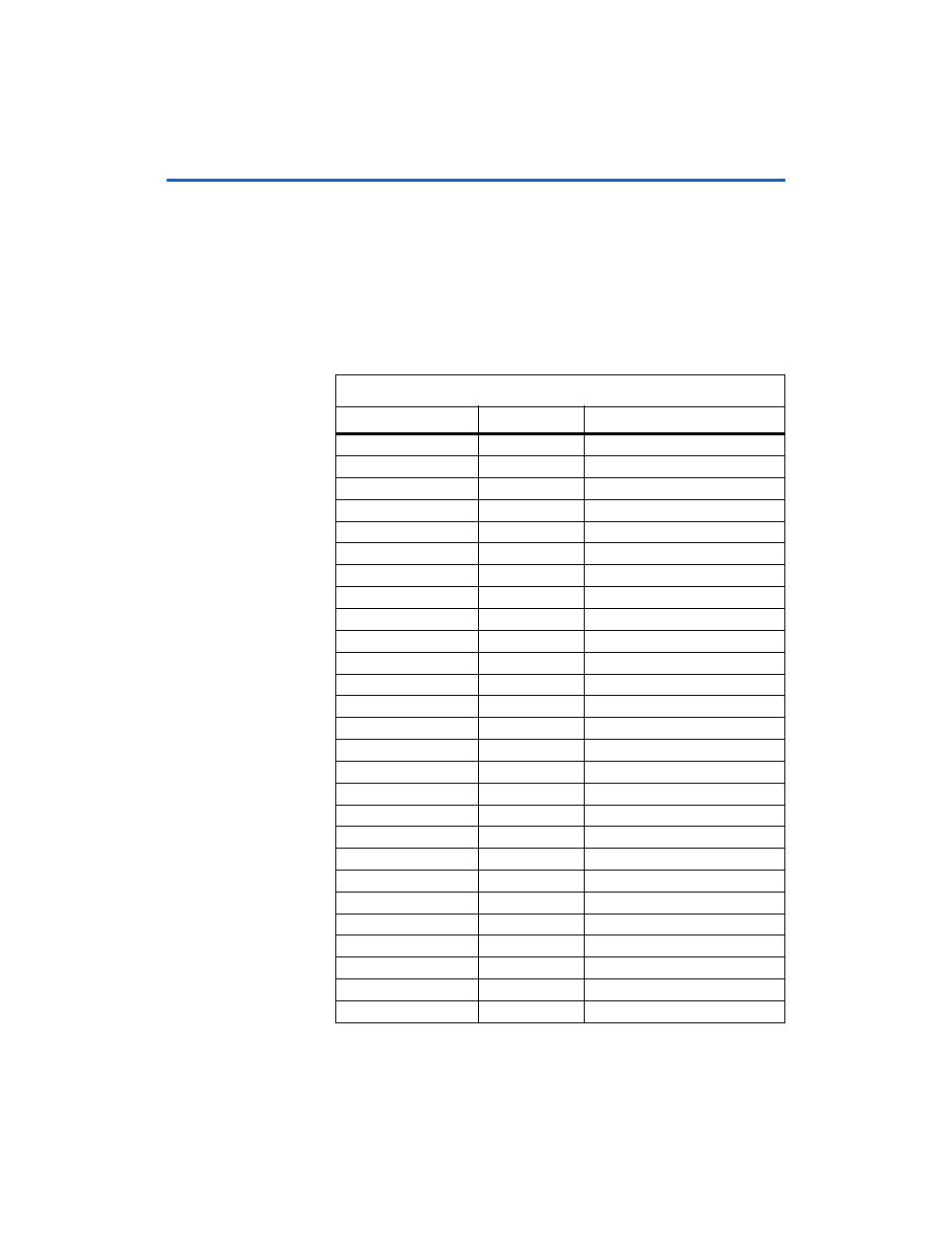

Table 2–5. SDRAM (U57) Pin Table (Part 1 of 2)

Pin Name

Pin Number

Connects to Stratix II Pin

A0

25

AD4

A1

26

AD3

A2

27

AD5

A3

60

W9

A4

61

W10

A5

62

AB10

A6

63

AF5

A7

64

AE5

A8

65

AC6

A9

66

AF6

A10

24

AA10

A11

21

Y9

BA0

22

AE23

BA1

23

AD23

DQ0

2

W15

DQ1

4

V14

DQ2

5

AA16

DQ3

7

AD16

DQ4

8

AF17

DQ5

10

AD17

DQ6

11

AF18

DQ7

13

AA17

DQ8

74

V16

DQ9

76

AB17

DQ10

77

AF19

DQ11

79

AD18

DQ12

80

AD19