Altera Nios Development Board User Manual

Page 30

2–22

Altera

Corporation

Nios Development Board Reference Manual, Stratix II Edition

July 2005

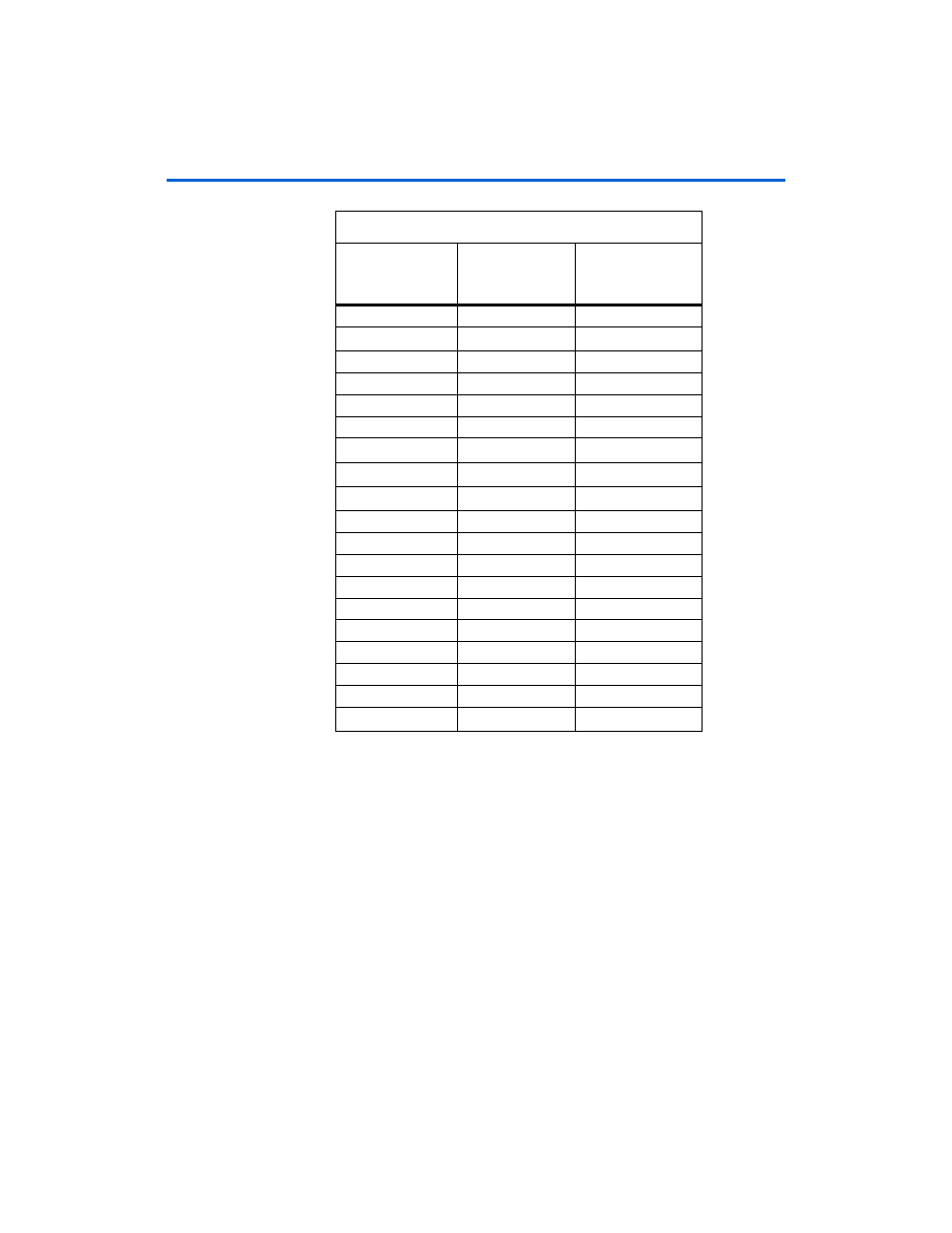

CompactFlash Connector (CON3)

f

For more information on the CompactFlash connector (CON3), refer to

www.compactflash.org

and www.molex.com.

32

-CE2

Y16

33

-VS1

GND

(3)

34

-OIORD

C7

35

-IOWR

A7

36

-WE

E10

37

RDY/BSY

J11

38

VCC

Y17

(

2)

39

-CSEL

GND

(3)

40

-VS2

no connect

(3)

41

RESET

(4)

42

-WAIT

D7

43

-INPACK

B7

44

-REG

B8

45

BVD2

G11

46

BVD1

C11

47

D081

J9

48

D091

A3

49

D101

C3

50

GND

GND

(3)

Note to

(1)

All pin numbers represent I/O pins on the FPGA, unless

otherwise noted.

(2)

This FPGA I/O pin controls a power MOSFET that supplies 5V

VCC to CON3.

(3)

This pin does not connect to the FPGA directly.

(4)

RESET is driven by the EPM7128AE configuration controller

device.

Table 2–6. CompactFlash (CON3) Pin Table (Part 2 of 2)

Pin on

CompactFlash

(CON3)

CompactFlash

Function (U60)

Connects to

(1)