Stratix ii device (u60), Stratix ii device (u60) –7 – Altera Nios Development Board User Manual

Page 15

Altera Corporation

2–7

July 2005

Nios Development Board Reference Manual, Stratix II Edition

Board Components

The sections that follow describe each component in detail.

Stratix II Device

(U60)

U60 is a Stratix II FPGA in a 672-pin FineLine BGA® package. Early

shipments of the Nios Development Board, Stratix II Edition included an

EP2S60F672C5 device. Some early boards used engineering sample parts,

indicated by “ES” after the part number. Later shipments of the board use

an EP2S30F672C5 device.

lists the device features.

SW8

CPU Reset button Push-button switch to reboot the Nios II processor configured

in the FPGA

SW9

Factory Config

button

Push-button switch to reconfigure the FPGA with the factory-

programmed reference design

SW10

Reset, Config

Push-button switch to reset the board

LED0 – LED3

Configuration

status LEDs

LEDs that display the current configuration status of the

FPGA

Clock Circuitry

Y2

Oscillator

50 MHz clock signal driven to FPGA

J4

External clock

input

Connector to FPGA clock pin

Power Supply

J26

DC power jack

17 V DC unregulated power source

D34

Bridge rectifier

Power rectifier allows for center-negative or center-positive

power supplies

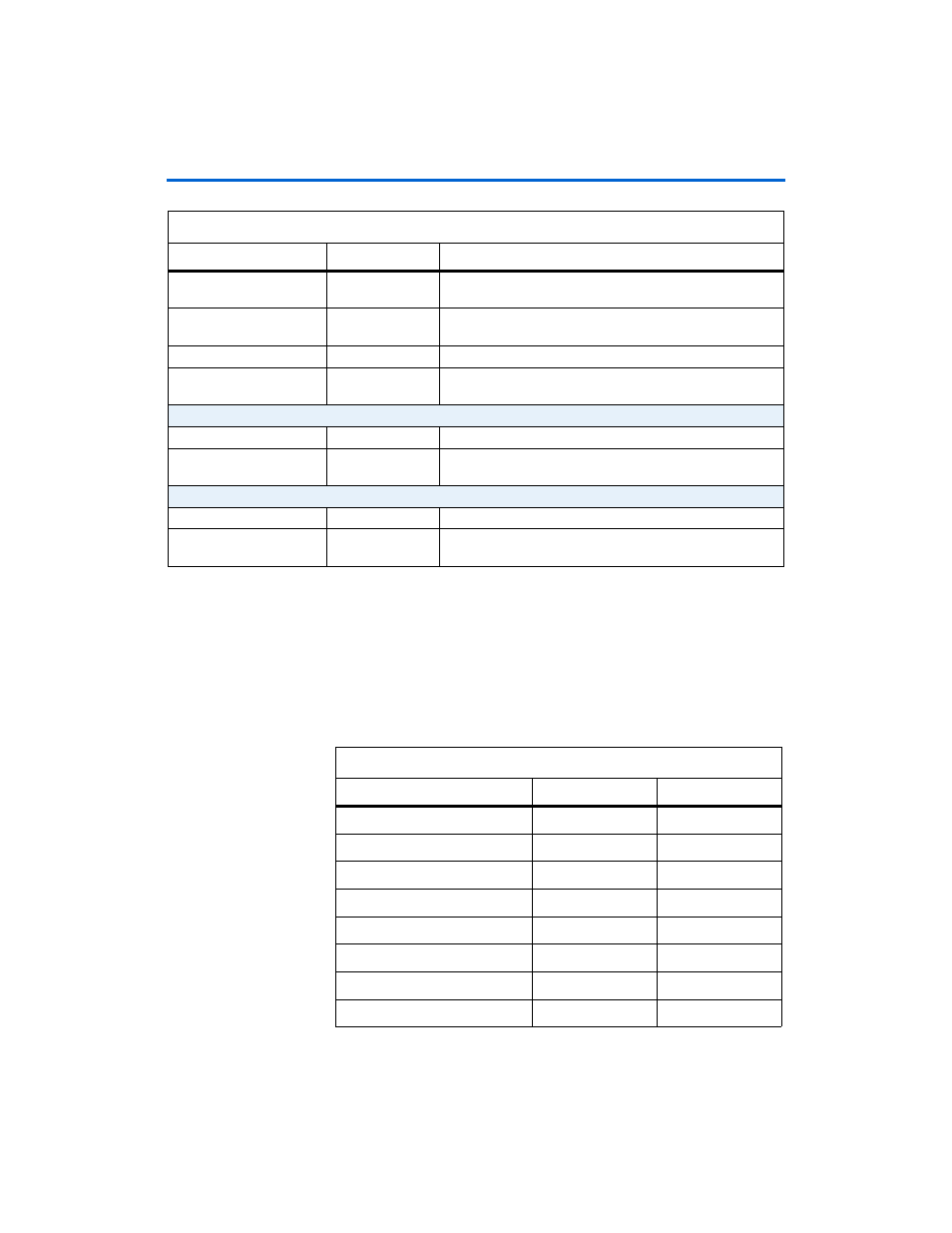

Table 2–1. Nios Development Board, Stratix Edition Components & Interfaces (Part 2 of 2)

Board Designation

Name

Description

Table 2–2. Stratix II Device Features (Part 1 of 2)

Feature

EP2S30

EP2S60

ALMs

13,552

24,176

Adaptive look-up tables (ALUTs)

27,104

48,352

Equivalent LEs

33,880

60,440

M512 RAM blocks

202

329

M4K RAM blocks

144

255

M-RAM blocks

1

2

Total RAM bits

1,369,728

2,544,192

DSP blocks

16

36