Altera Transceiver PHY IP Core User Manual

Page 197

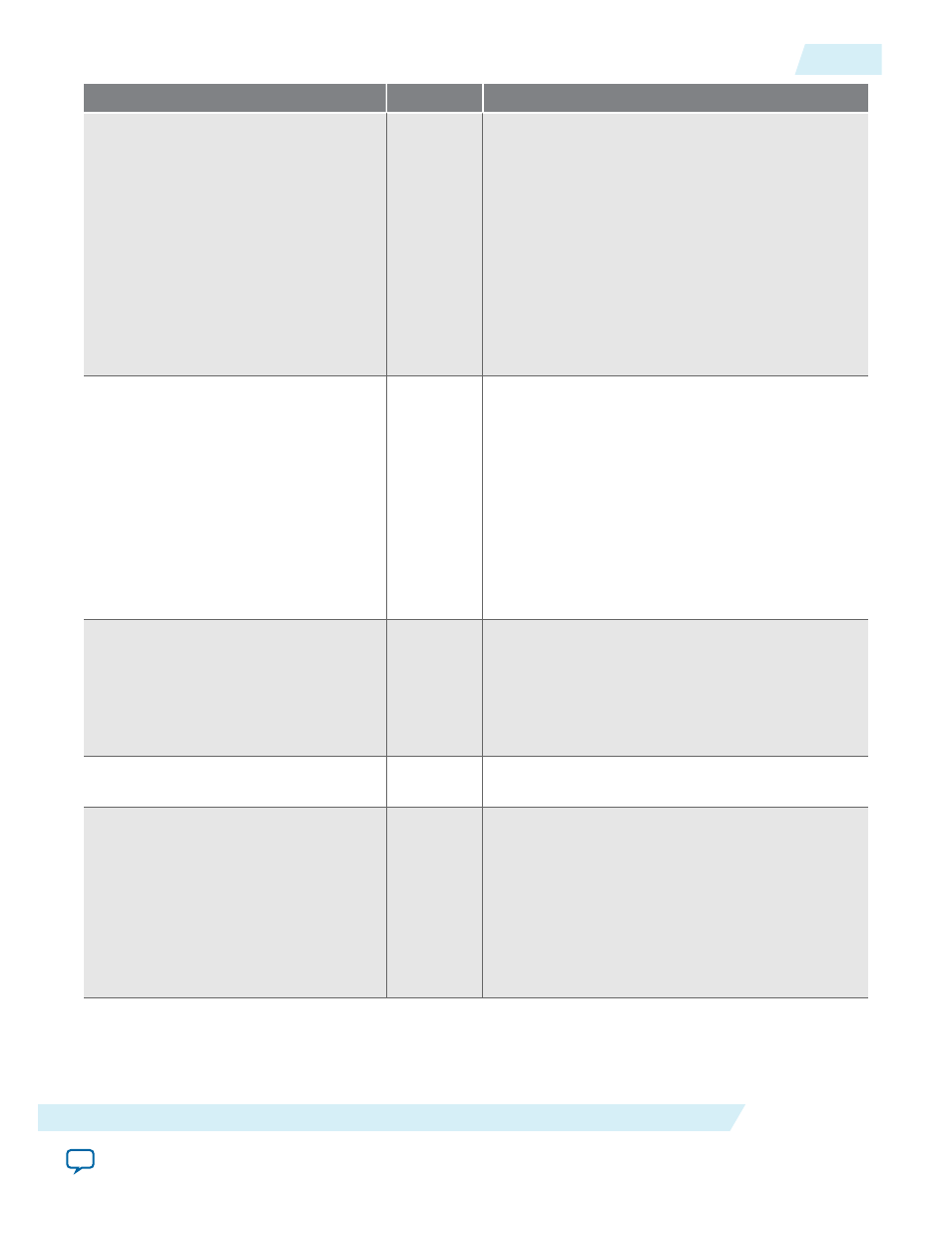

Signal Name

Direction

Description

pipe_g3_txdeemph[17:0]

Input

For Gen3, selects the transmitter de-emphasis. The

18 bits specify the following coefficients:

• [5:0]: C

-1

• [11:6]: C

0

• [17:12]: C

+1

for presets to TX de-emphasis

mappings.

In Gen3 capable designs, the TX deemphasis for

Gen2 data rates is always -6 dB. The TX

deemphasis for Gen1 data rate is always -3.5 dB.

pipe_txmargin[3<n>-1:0]

Input

Transmit V

OD

margin selection. The MAC PHY

sets the value for this signal based on the value

from the Link Control 2 Register. The following

encodings are defined:

• 3'b000: Normal operating range

• 3'b001: Full swing: 800 - 1200 mV; Half swing:

400 - 700 mV

• 3'b010:–3’b011: Reserved

• 3'b100–3’b111: If last value, full swing: 200 - 400

mV, half swing: 100 - 200 mV else reserved

pipe_txswing

Input

Indicates whether the transceiver is using full- or

low-swing voltages as defined by the

tx_

pipemargin

.

• 1’b0–Full swing.

• 1’b1–Low swing.

pipe_rxpolarity

Input

When 1, instructs the PHY layer to invert the

polarity on the received data.

pipe_rate[1:0]

Input

The 2-bit encodings have the following meanings:

• 2’b00: Gen1 rate (2.5 Gbps)

• 2’b01: Gen2 rate (5.0 Gbps)

• 2’b1x: Gen3 (8.0 Gbps)

The Rate Switch from Gen1 to Gen2 Timing

Diagram illustrates the timing of a rate switch from

Gen1 to Gen2 and back to Gen1.

UG-01080

2015.01.19

PHY for PCIe (PIPE) Input Data from the PHY MAC

8-9

PHY IP Core for PCI Express (PIPE)

Altera Corporation