Altera Transceiver PHY IP Core User Manual

Page 683

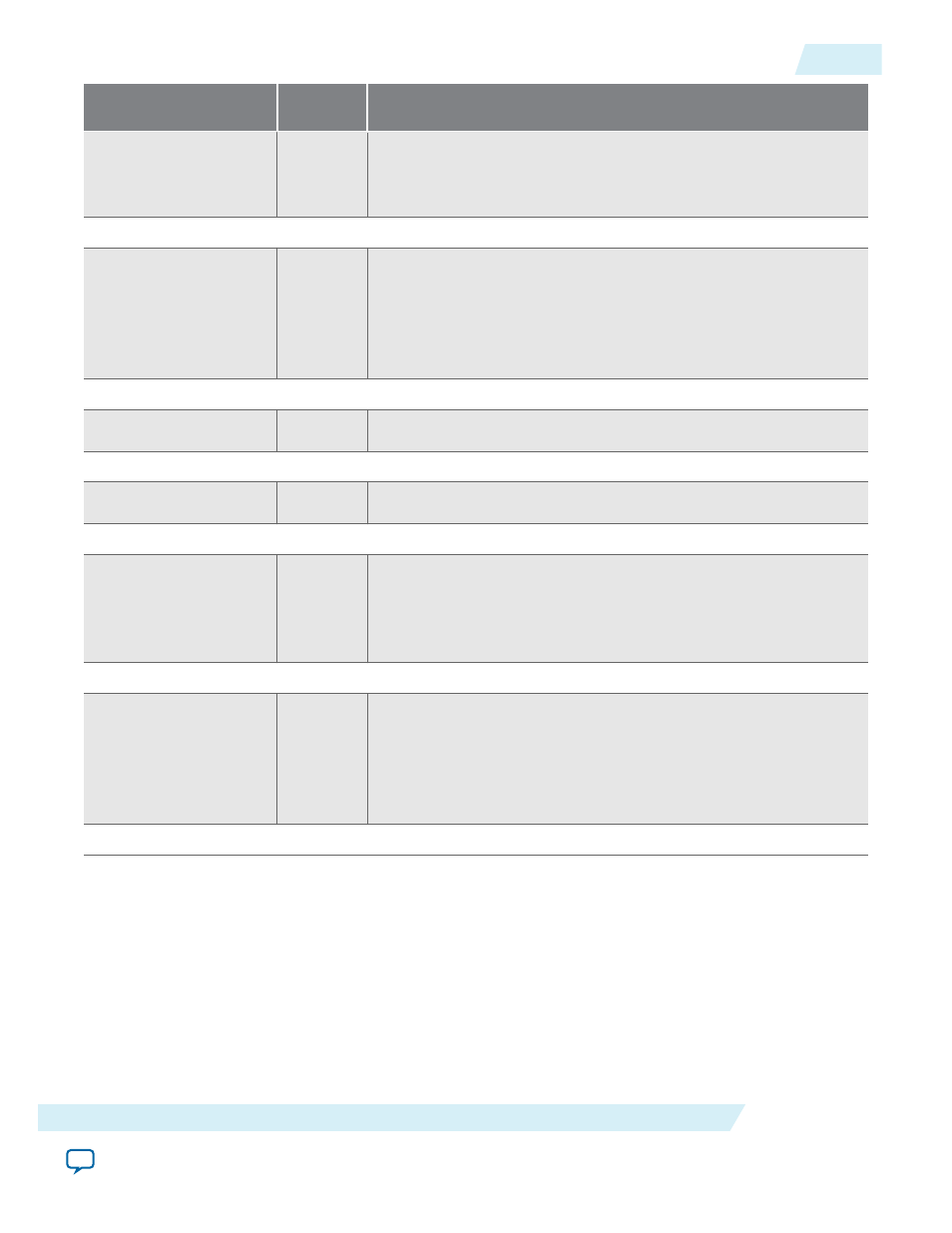

Date

Document

Version

Changes Made

November 2012

1.8

• Expanded discussion of the Arria V, Arria V GZ, Cyclone V, and

Stratix V Transceiver Native PHY IP Cores.

• Added Riviera-PRO Aldec simulation directory.

10GBASE-R PHY

November 2012

1.8

• Added support for IEEE 1588 Precision Time Protocol.

• Added Arria V GZ support.

• Enabled

RCLR_BER_COUNT

(0x81, bit 3) and

HI_BER

(0x82, bit 1)

for Arria V GZ and Stratix V devices.

• Moved Analog Options to a separate chapter.

10GBASE-KR PHY

November 2012

1.8

• Initial release.

1G/10 Gbps Ethernet PHY

November 2012

1.8

• Initial release.

XAUI PHY

November 2012

1.8

• Added Arria V GZ support.

• Moved Analog Options to a separate chapter.

• Added constraint for

tx_digitalreset

when TX PCS uses

bonded clocks.

Interlaken PHY

November 2012

1.8

• Added Arria V GZ support.

• Added 12500 Mbps lane rate.

• Moved Analog Options to a separate chapter.

• Removed recommendation to use /40 for

tx_user_clkout

and

rx_coreclkin

. Data rates between /40 and /67 all work reliably.

PHY IP Core for PCI Express (PIPE)

UG-01080

2015.01.19

Revision History for Previous Releases of the Transceiver PHY IP Core

21-23

Additional Information for the Transceiver PHY IP Core

Altera Corporation