10gbase-kr phy data interfaces, 10gbase-kr phy data interfaces -22 – Altera Transceiver PHY IP Core User Manual

Page 78

•

Transceiver Reconfiguration Controller IP Core Overview

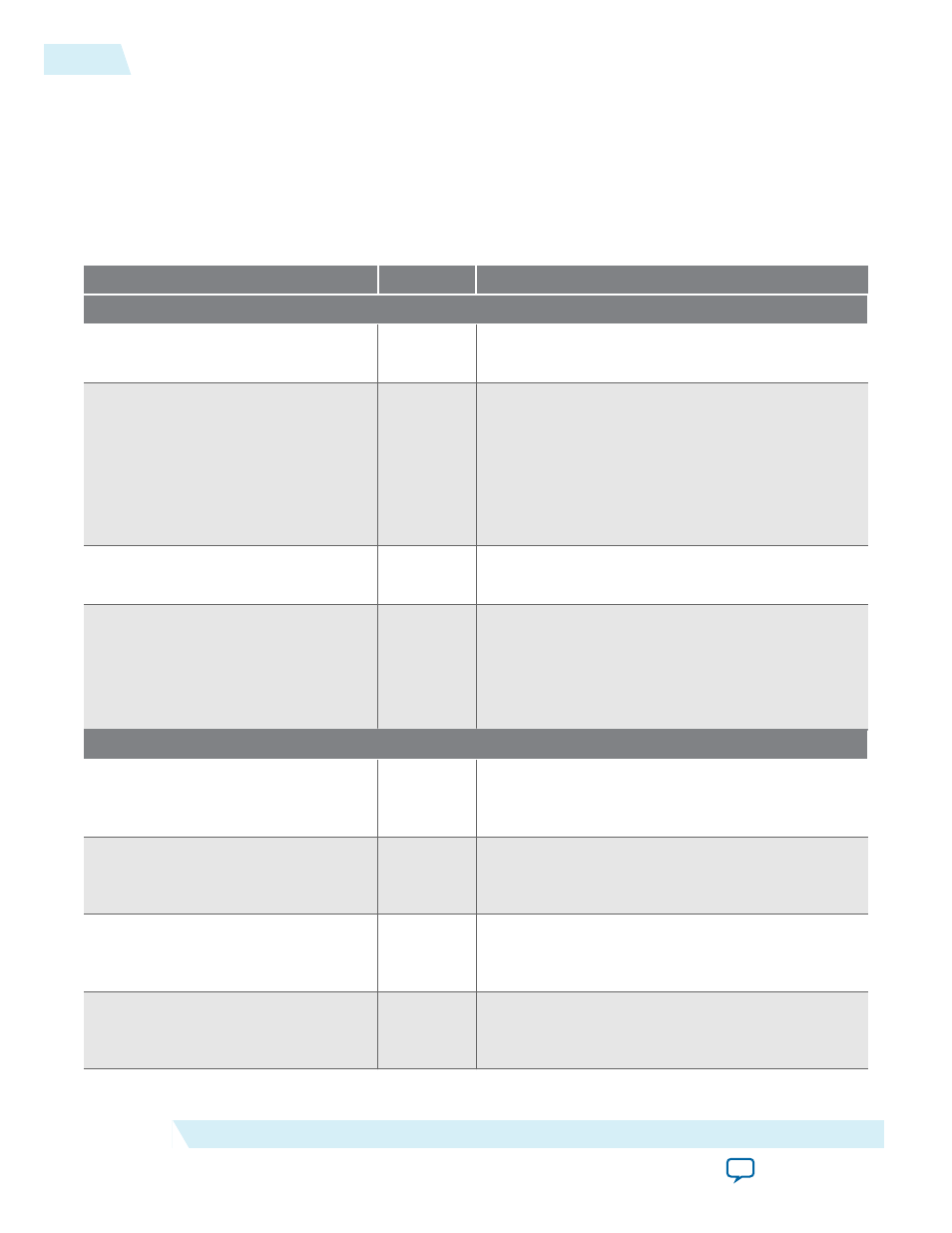

10GBASE-KR PHY Data Interfaces

The following table describes the signals in the XGMII and GMII interfaces. The MAC drives the TX

XGMII and GMII signals to the 10GBASE-KR PHY. The 10GBASE-KR PHY drives the RX XGMII or

GMII signals to the MAC.

Table 4-11: XGMII and GMII Signals

Signal Name

Direction

Description

10GBASE-KR XGMII Data Interface

xgmii_tx_dc[71:0]

Input

XGMII data and control for 8 lanes. Each lane

consists of 8 bits of data and 1 bit of control.

xgmii_tx_clk

Input

Clock for single data rate (SDR) XGMII TX

interface to the MAC. It should connect to

xgmii_

rx_clk

. The frequency is 156.25 MHz irrespective

of 1588 being enabled or disabled. Driven from the

MAC.

This clock is derived from the transceiver reference

clock (

pll_ref_clk_10g

).

xgmii_rx_dc[71:0]

Output

RX XGMII data and control for 8 lanes. Each lane

consists of 8 bits of data and 1 bit of control.

xgmii_rx_clk

Input

Clock for SDR XGMII RX interface to the MAC.

The frequency is 156.25 MHz irrespective of 1588

being enabled or disabled. Driven from the MAC.

This clock is derived from the transceiver reference

clock (

pll_ref_clk_10g

).

10GBASE-KR GMII Data Interface

gmii_tx_d[7:0]

Input

TX data for 1G mode. Synchronized to

tx_clkout_

1g

clock. The TX PCS 8B/10B module encodes this

data which is sent to link partner.

gmii_rx_d[7:0]

Output

RX data for 1G mode. Synchronized to

rx_clkout_

1g

clock. The RX PCS 8B/10B decoders decodes this

data and sends it to the MAC.

gmii_tx_en

Input

When asserted, indicates the start of a new frame. It

should remain asserted until the last byte of data on

the frame is present on

gmii_tx_d

.

gmii_tx_err

Input

When asserted, indicates an error. May be asserted

at any time during a frame transfer to indicate an

error in that frame.

4-22

10GBASE-KR PHY Data Interfaces

UG-01080

2015.01.19

Altera Corporation

Backplane Ethernet 10GBASE-KR PHY IP Core with Early Access FEC Option