Altera Transceiver PHY IP Core User Manual

Page 218

Name

Value

Description

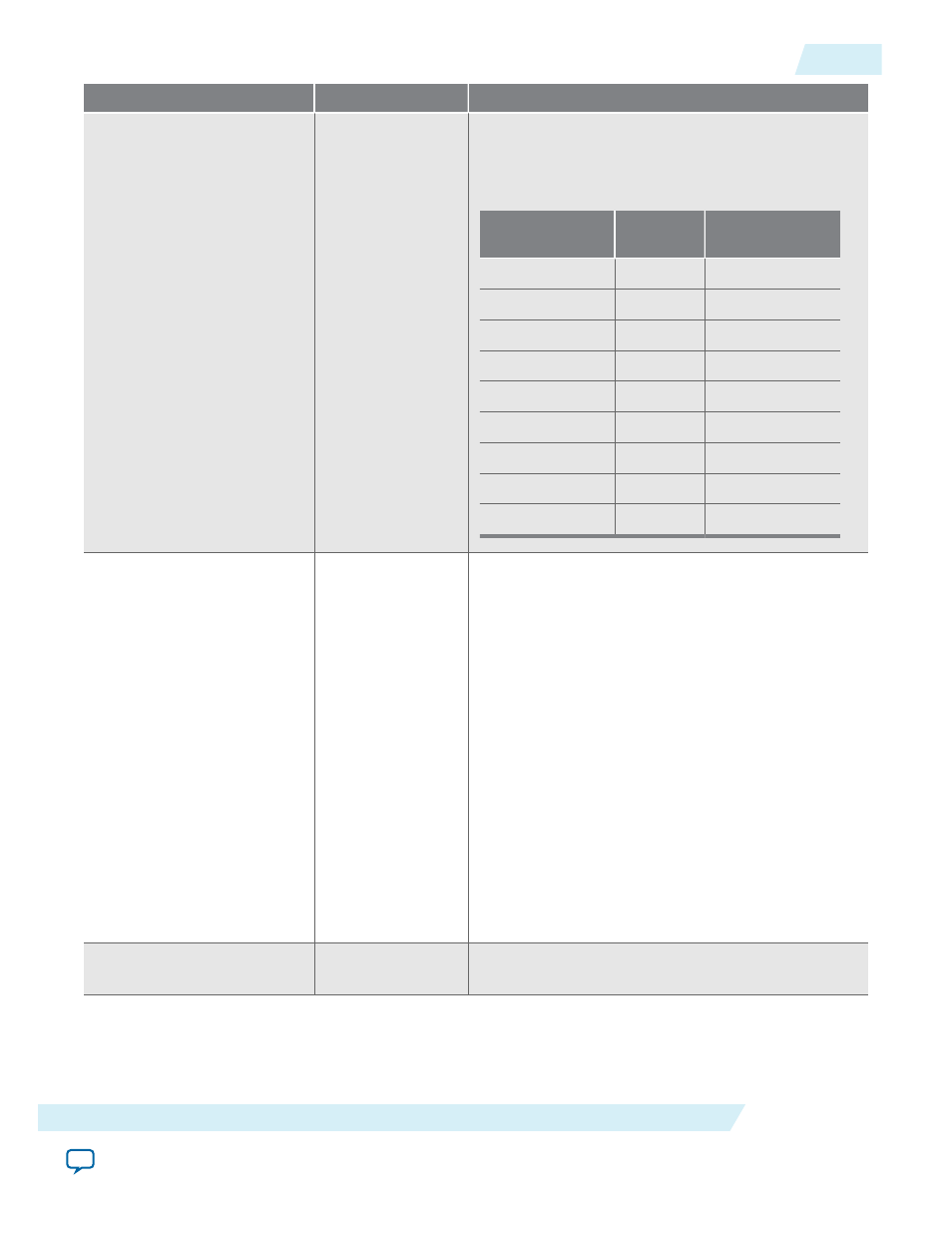

PCS-PMA interface width 8, 10, 16, 20

The PCS-PMA interface width depends on the

FPGA fabric transceiver interface width and whether

8B/10B is enabled. The following combinations are

available:

FPGA/XCVR

8B/10B

PMA Interface

Width

8

No

8

8

Yes

10

10

No

10

16

No

8 or 16

16

Yes

10 or 20

20

No

10 or20

32

No

16

32

Yes

20

40

No

20

PLL type

CMU ATX

The CMU PLL is available for Arria V and Cyclone V

devices.

For Stratix V devices, you can select either the CMU

or ATX PLL. The CMU PLL has a larger frequency

range than the ATX PLL. The ATX PLL is designed

to improve jitter performance and achieves lower

channel-to-channel skew; however, it supports a

narrower range of data rates and reference clock

frequencies. Another advantage of the ATX PLL is

that it does not use a transceiver channel, while the

CMU PLL does.

Because the CMU PLL is more versatile, it is

specified as the default setting. An informational

message displays in the message pane telling you

whether the chosen settings for Data rate and Input

clock frequency are legal for the CMU PLL, or for

both the CMU and ATX PLLs.

Data rate

622-11000 Mbps

Specifies the data rate. The possible data rates depend

upon the device and configuration specified.

UG-01080

2015.01.19

General Options Parameters

9-5

Custom PHY IP Core

Altera Corporation