BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 109

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-97

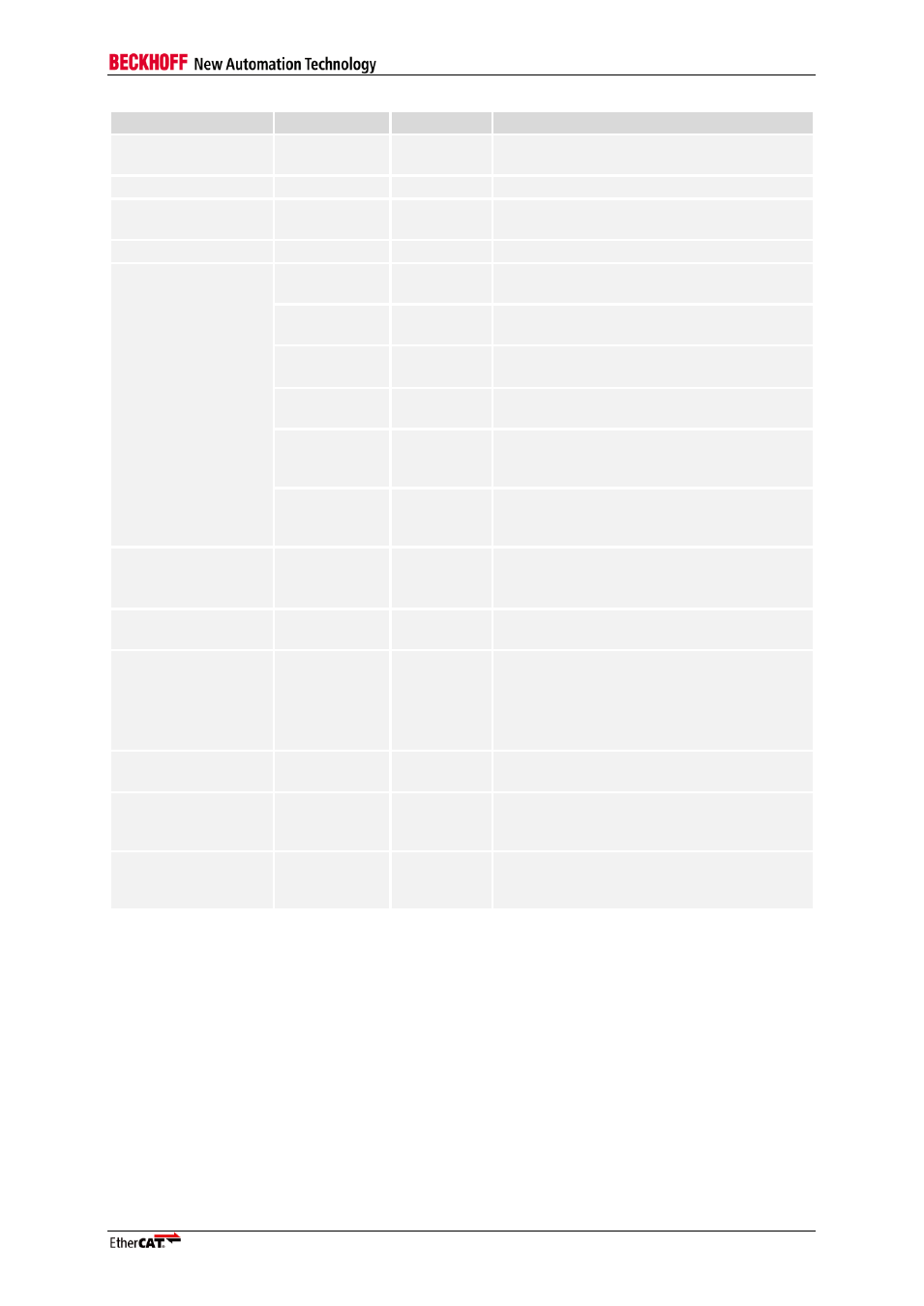

Parameter

Min

Max

Comment

t

ADR_BHE_DATA_hold

ADR, BHE and Write DATA valid after WR

deassertion

t

WR_active

WR assertion time

t

BUSY_to_WR_CS

WR or CS deassertion after BUSY

deassertion

t

WR_to_BUSY

BUSY assertion after WR deassertion

t

write

0 ns

External write time (WR assertion to BUSY

deassertion)

a) t

write_int

a) Configuration: write after falling edge of

WR (act. low)

b) t

write_int

-t

WR_delay

b) with preceding write access and t

WR_delay

< t

write_int

(Write after rising edge of WR)

c) 0 ns

c) without preceding write access or t

WR_delay

≥ t

write_int

(Write after rising edge of WR)

d) 180 ns

d) 8 bit access, absolute worst case with

preceding write access (t

WR_delay

= min,

t

WR_int

=max, Write after rising edge of WR)

e) 260 ns

e) 16 bit access, absolute worst case with

preceding write access (t

WR_delay

=min,

t

WR_int

=max, Write after rising edge of WR)

t

write_int

a) 180 ns

b) 260 ns

Internal write time

a) 8 bit access

b) 16 bit access

t

WR_delay

Delay between WR deassertion and

assertion

t

Coll

a) 20 ns

b) 0 ns

Extra read delay

a) RD access directly follows WR access

with the same address (8 bit accesses or 8

bit WR and 16 bit RD)

b) different addresses or 16 bit accesses

t

WR_to_RD

0 ns

Delay between WR deassertion and RD

assertion

t

CS_WR_overlap

Time both CS and WR have to be

deasserted simultaneously (only if CS is

deasserted at all)

t

CS_RD_overlap

Time both CS and RD have to be

deasserted simultaneously (only if CS is

deasserted at all)