4 timing specifications, Timing specifications, Table 58: opb timing characteristics – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 118

Advertising

PDI Description

III-106

Slave Controller

– IP Core for Xilinx FPGAs

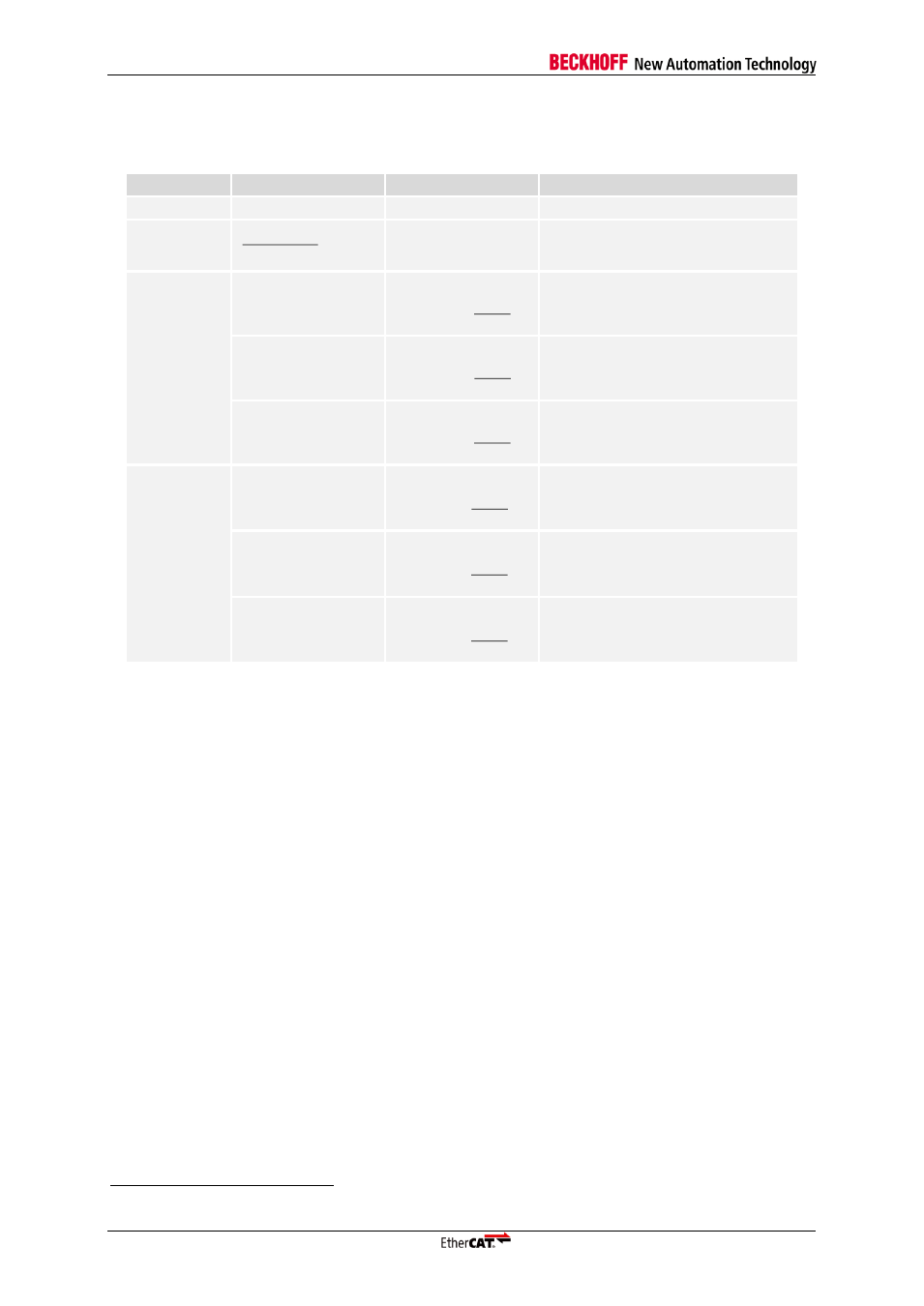

10.5.4 Timing specifications

Table 58: OPB timing characteristics

Parameter

Min

Max

Comment

N

1

31

OPB bus clock factor

t

Clk

MHz

25

*

N

1

15

40 ns

OPB bus clock

(OPB clock frequency: N*25 MHz)

t

Read

440 ns

a) 560 ns

b)

N

ns

80

ns

560

32 Bit read access time

a) N=1

b) N>1

280 ns

a) 400 ns

b)

N

ns

80

ns

400

16 Bit read access time

a) N=1

b) N>1

200 ns

a) 320 ns

b)

N

ns

80

ns

320

8 Bit read access time

a) N=1

b) N>1

t

Write

360 ns

a) 440 ns

b)

N

ns

80

ns

440

32 Bit write access time

a) N=1

b) N>1

200 ns

a) 280 ns

b)

N

ns

80

ns

280

16 Bit write access time

a) N=1

b) N>1

120 ns

a) 200 ns

b)

N

ns

80

ns

200

8 Bit write access time

a) N=1

b) N>1

15

EtherCAT IP Core: time depends on synthesis results

Advertising

This manual is related to the following products: