5 physical layer interface, Physical layer interface, Table 22: physical layer general – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 68

IP Core Signals

III-56

Slave Controller

– IP Core for Xilinx FPGAs

8.5

Physical Layer Interface

The IP Core is connected with Ethernet PHYs using MII or RMII interfaces.

Table 22 lists the general PHY interface signals.

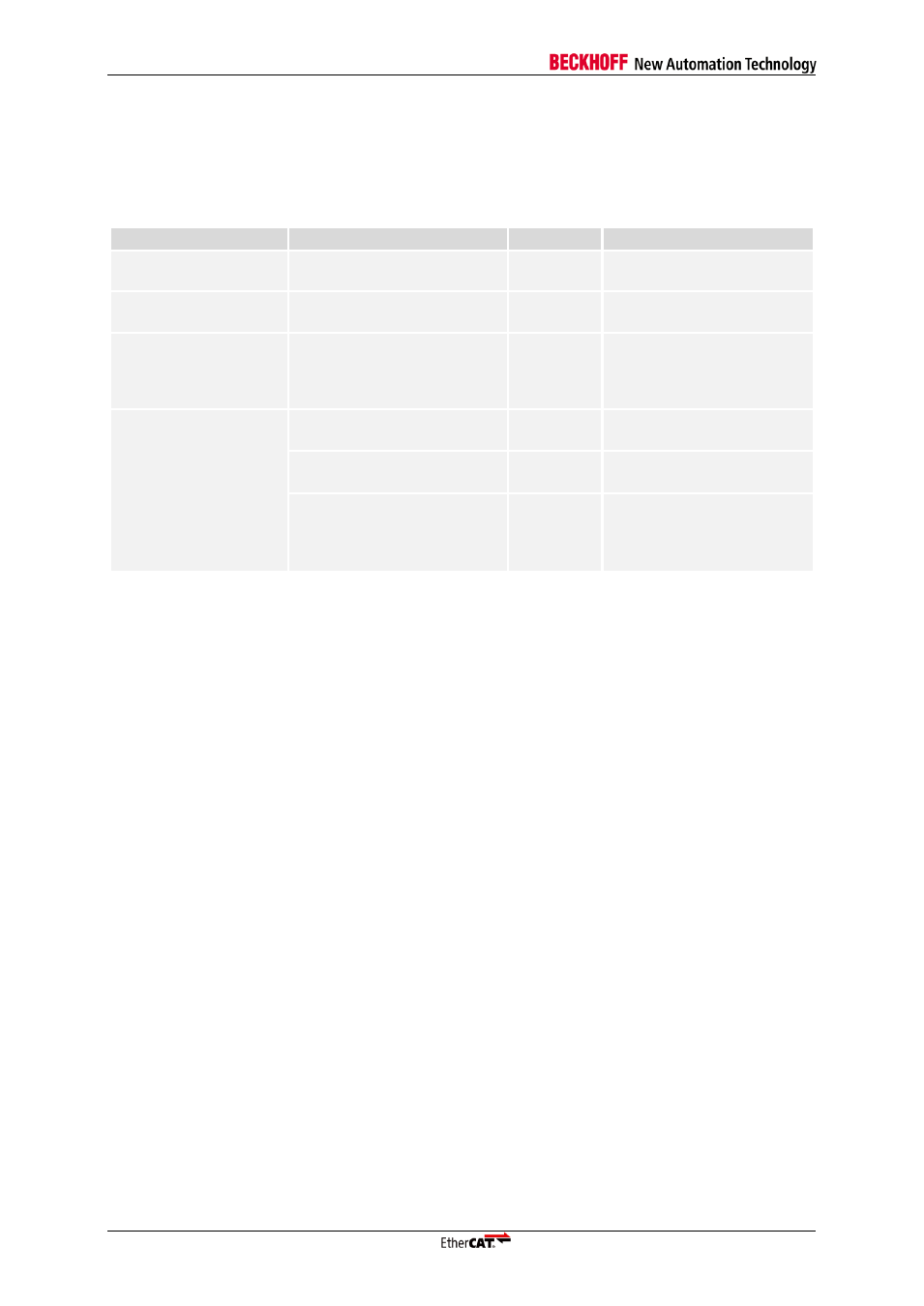

Table 22: Physical Layer General

Condition

Name

Direction

Description

PHY Management

Interface enabled

PHY_OFFSET_VEC[4:0]

INPUT

PHY address offset

PHY Management

Interface enabled

MCLK

OUTPUT

PHY management clock

PHY Management

Interface enabled,

Tristate drivers inside

core (EEPROM/MII)

MDIO

BIDIR

PHY management data

PHY Management

Interface enabled,

External tristate drivers

for EEPROM/MI

MDIO_DATA_IN

INPUT

PHY management data:

PHY IP Core

MDIO_DATA_OUT

OUTPUT

PHY management data:

IP Core PHY

MDIO_DATA_ENA

OUTPUT

0: disable output driver for

MDIO_DATA_OUT

1: enable output driver for

MDIO_DATA_OUT

NOTE: MDIO must have a pull-up resistor (4.7k

Ω recommended for ESCs).