Figure 38: digital output timing, Figure 39: out_ena timing – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 92

Advertising

PDI Description

III-80

Slave Controller

– IP Core for Xilinx FPGAs

SOF

DATA

Input DATA

t

SOF_to_DATA_setup

t

SOF

t

SOF_to_DATA_hold

Figure 36: Digital Input: Input data sampled at SOF, I/O can be read in the same frame

LATCH_IN

DATA

Input DATA

t

DATA_hold

t

DATA_setup

t

LATCH_IN

t

Input_event_delay

Figure 37: Digital Input: Input data sampled with LATCH_IN

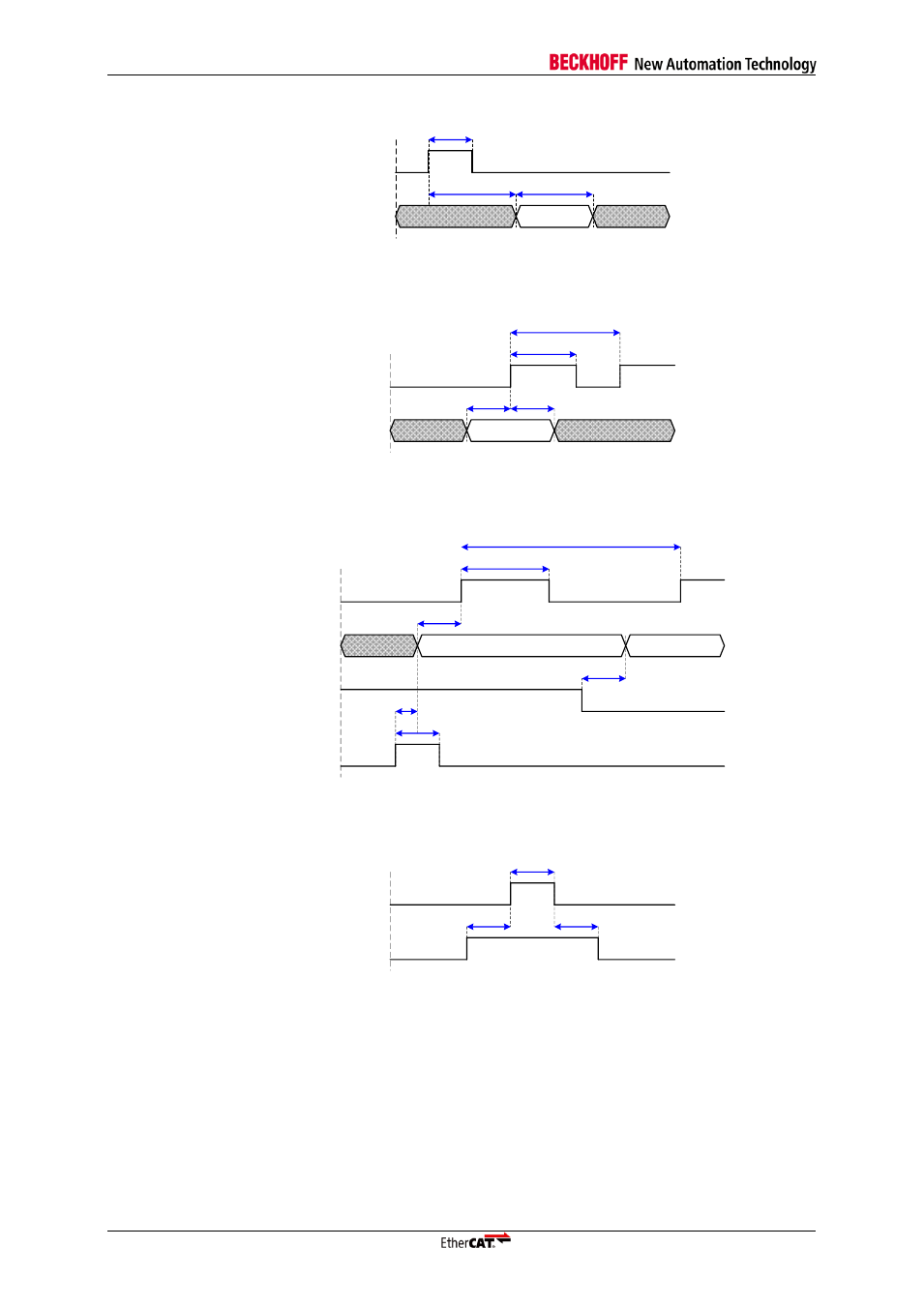

OUTVALID

DATA

t

DATA_to_OUTVALID

Output DATA

t

OUTVALID

Zero or High-Impedance

t

OE_EXT_to_DATA_invalid

OE_EXT

WD_TRIG

t

WD_TRIG

t

DATA_to_WD_TRIG

t

output_event_delay

Figure 38: Digital Output timing

OUTVALID

t

OUT_ENA_valid

t

OUT_ENA_invalid

t

OUTVALID

OUT_ENA

Figure 39: OUT_ENA timing

Advertising

This manual is related to the following products: