6 opb on-chip peripheral bus, Opb on-chip peripheral bus, Table 32: opb pdi – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 77

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-65

8.6.6

OPB On-Chip Peripheral Bus

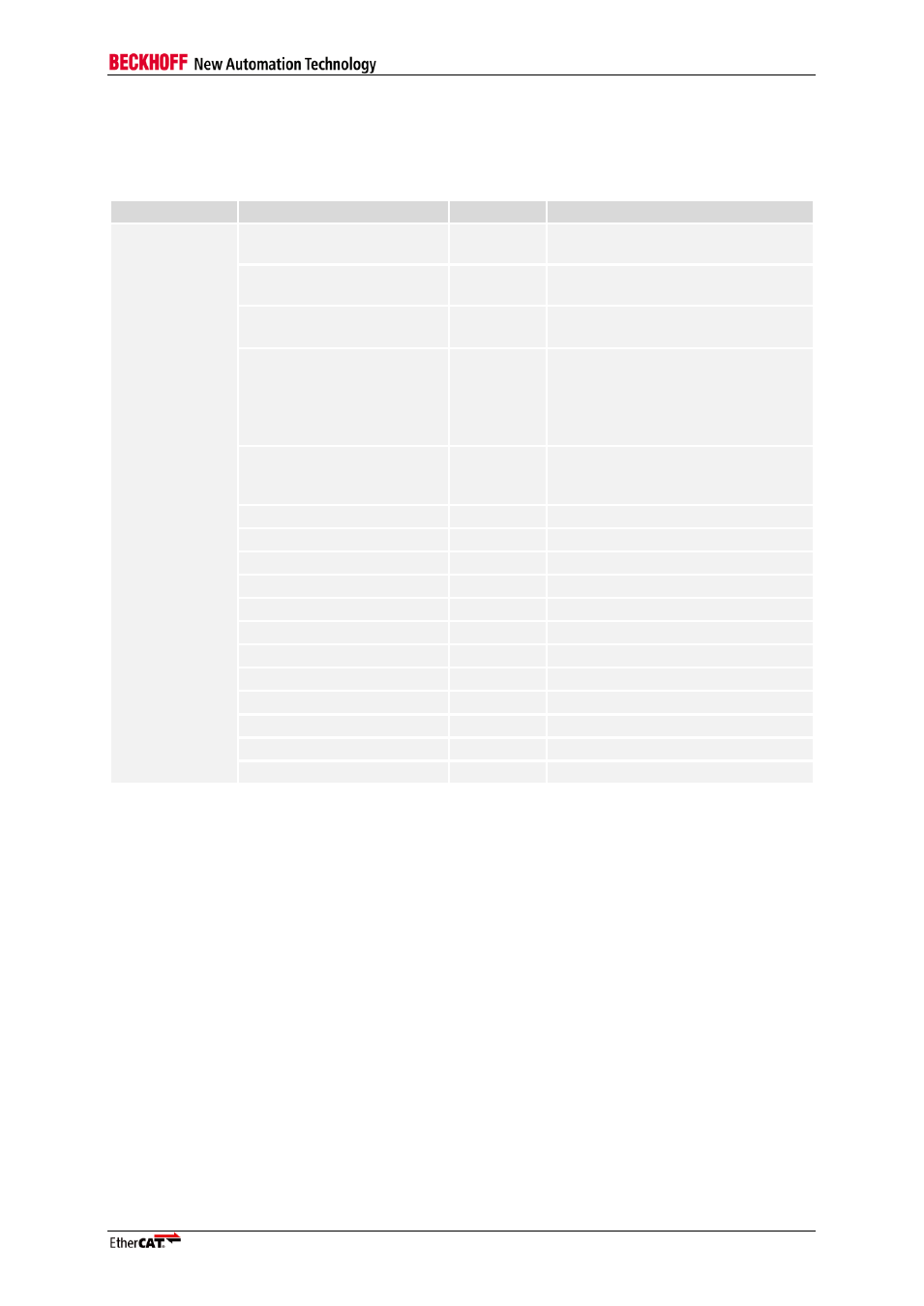

Table 32 lists the signals used with the OPB PDI.

Table 32: OPB PDI

Condition

Name

Direction

Description

OPB PDI

C_BASEADDR

GENERIC

OPB base address of the IP core

address range

C_HIGHADDR

GENERIC

OPB end address of the IP core

address range

RESET_POL_ACT_HIGH

GENERIC

0: nReset polarity is active low

1: nReset polarity is active high

PDI_EMULATION

INPUT

Value for register 0x0140.8:

0: device status register is

controlled by µC

1: device status register is identical

to device control register

PDI_OPB_CLK

INPUT

N*25 MHz OPB bus clock from DLL

(rising edge of CLK25 synchronous

with rising edge of PDI_OPB_CLK)

PDI_OPB_ABUS[0:31]

INPUT

OPB address bus

PDI_OPB_DBUS[0:31]

INPUT

OPB data bus

PDI_OPB_BE[0:3]

INPUT

OPB byte enable

PDI_OPB_RNW

INPUT

OPB read/write access

PDI_OPB_SELECT

INPUT

OPB select

PDI_OPB_SEQADDR

INPUT

OPB sequential address

PDI_OPB_SL_DBUS[0:31]

OUTPUT

Slave data bus

PDI_OPB_SL_ERRACK

OUTPUT

Slave error acknowledge

PDI_OPB_SL_RETRY

OUTPUT

Slave bus cycle retry

PDI_OPB_SL_TOUTSUP

OUTPUT

Slave timeout suppress

PDI_OPB_SL_XFERACK

OUTPUT

Slave transfer acknowledge

PDI_OPB_IRQ

OUTPUT

Slave interrupt output

The address range of the EtherCAT IP core should span at least 64 Kbyte (e.g., C_BASEADDR =

0x00010000 and C_HIGHADDR=0x0001FFFF). A larger address range results in less address

decoding logic.