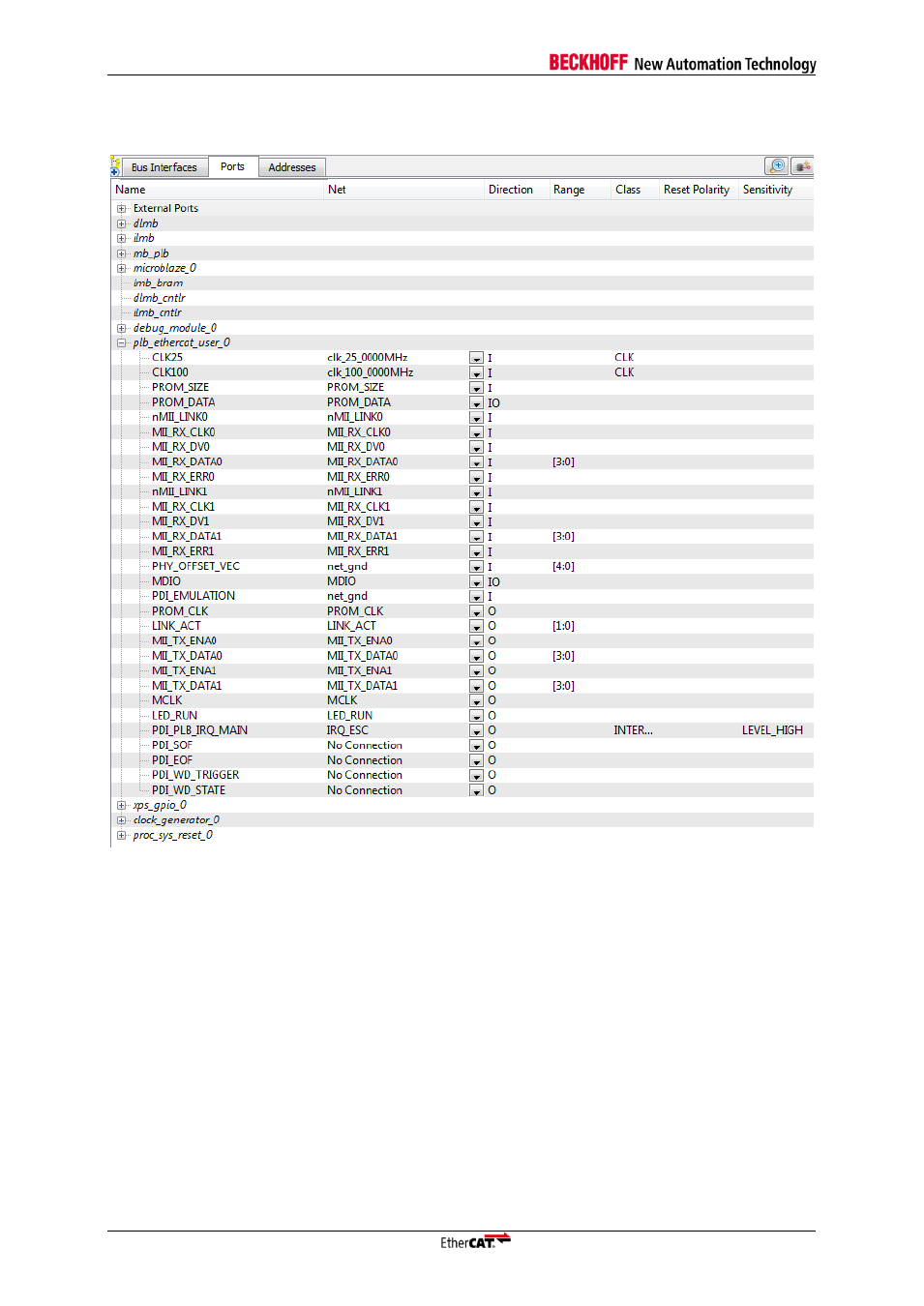

Figure 11: edk, System assembly view, ports tab – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 42

Advertising

This manual is related to the following products: