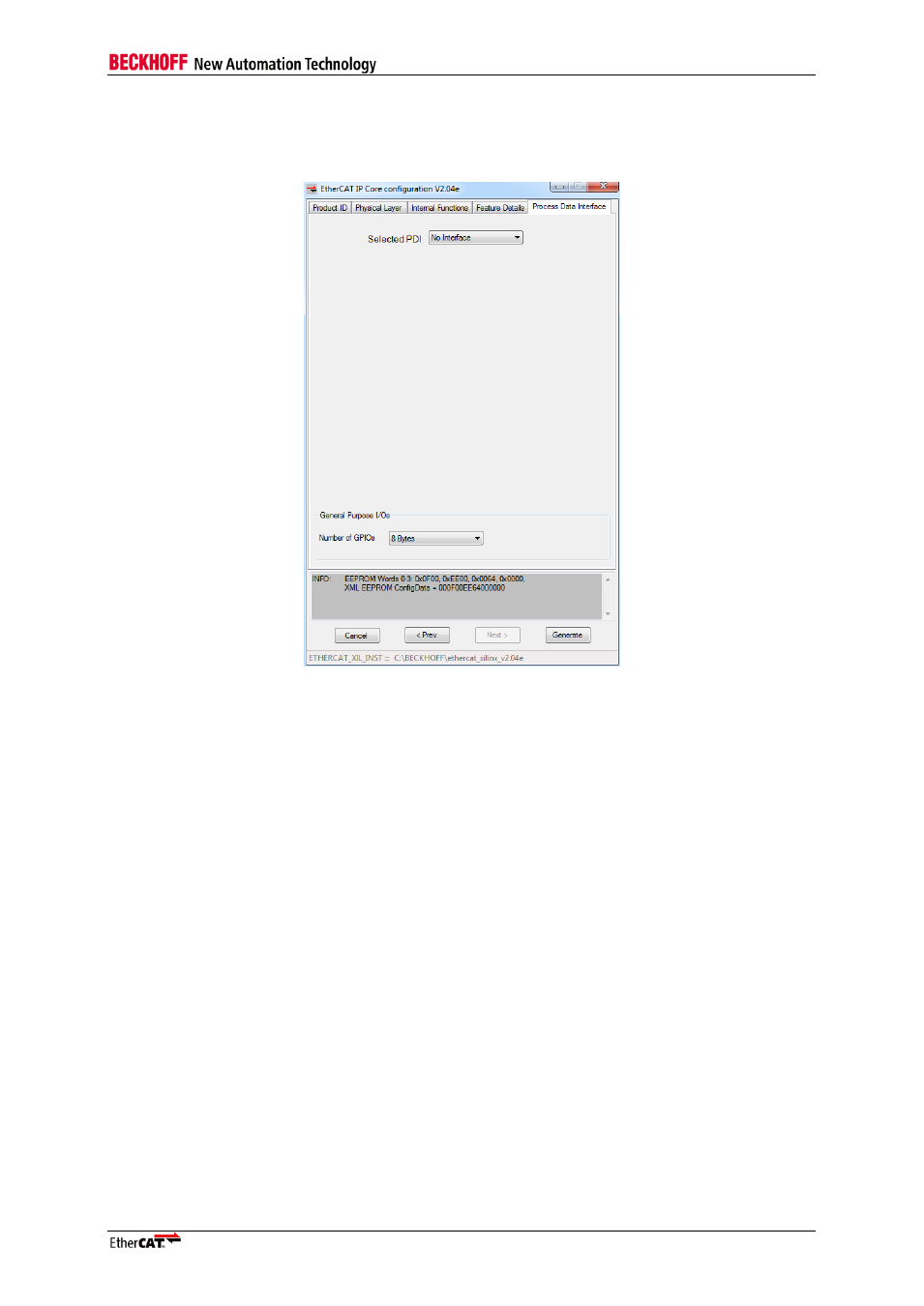

1 no interface and general purpose i/o, Figure 18: register process data interface – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 51

Advertising

IP Core Configuration

Slave Controller

– IP Core for Xilinx FPGAs

III-39

5.1.5.1

No Interface and General Purpose I/O

If there is no interface selected no communication with the application is possible (except for general

purpose I/O).

Figure 18: Register Process Data Interface

Number of GPIOs

General purpose I/O signals can be added to any selected PDI. The number of GPIO bytes is

configurable to 0, 1, 2, 4, or 8 Bytes. Both general purpose outputs and general purpose inputs of the

selected width are available.

Advertising

This manual is related to the following products: