Verilink SCC 2020 (880-503268-001) Product Manual User Manual

Page 70

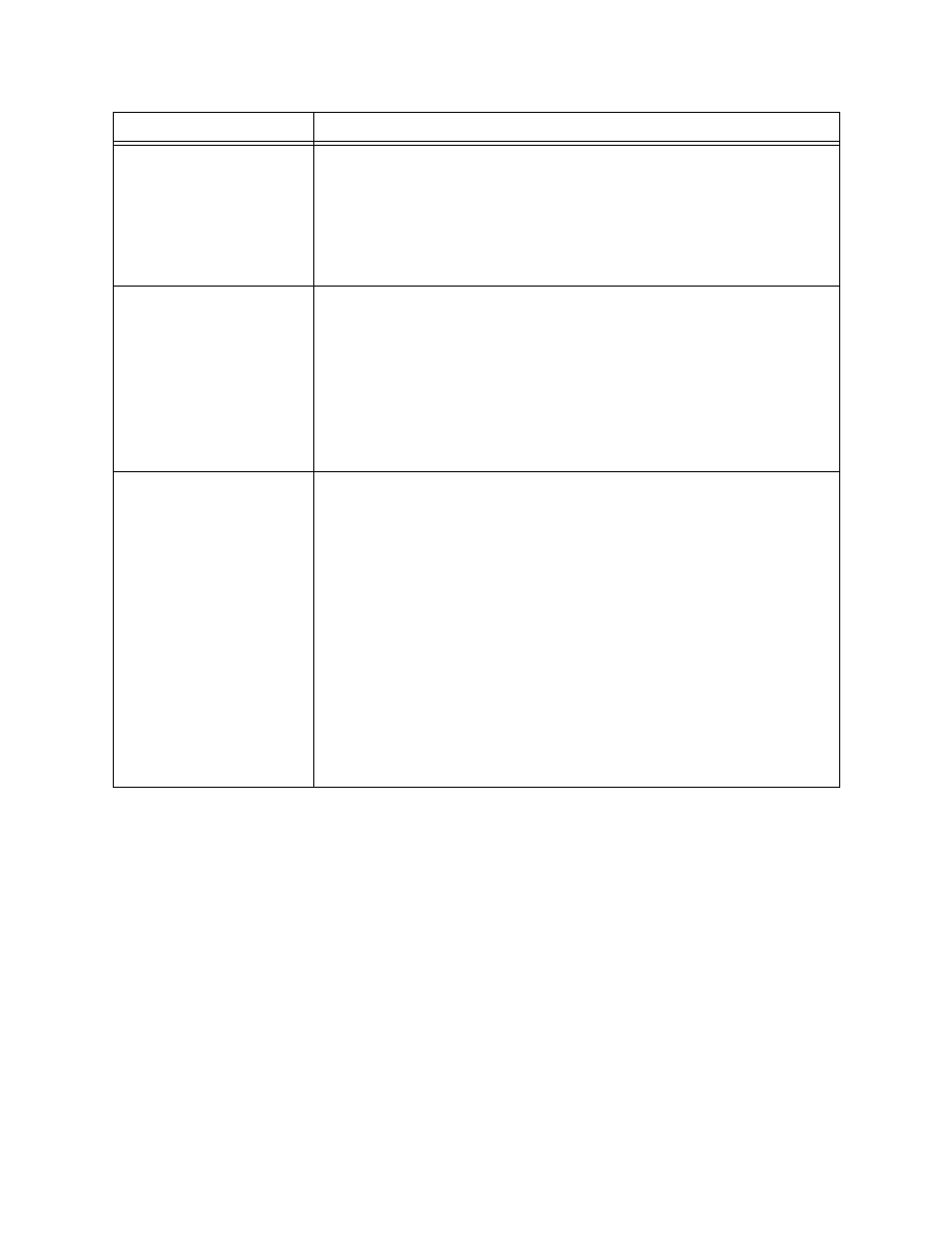

Diagnostics

5-12

Verilink SCC 2020 User Manual

Loopback Plug

For a completely reliable test of a CSU, make a T1 loopback plug

and plug it in to the network port. The CSU will now receive the

signals it is sending.

If the CSU is sending a defective signal, it will receive a defective

signal and declare an alarm. If the receive circuitry is defective,

such that it cannot decode a good signal, it will be unable to decode

the signal it is transmitting and will declare an alarm. Thus, if a T1

CSU does not declare any alarms with a loopback plug in lieu of the

T1 circuit, the CSU is not defective. This does not rely on any tests

built in to the product, thereby producing a higher confidence level

in the results of the test.

Alarm

— when a Verilink AS 2000 CSU reports “ALARM” in the Craft interface, it is

receiving a yellow alarm (RAIS) on that port

— T1 devices send a yellow alarm to alert the far end device when they are

in a red alarm condition such as: Loss Of Signal(LOS), Loss Of Frame(LOF),

or Alarm Indication Signal(AIS - received all ones keep-alive)

— to resolve a problem with received yellow alarms, find the trouble in the

transmit path of the CSU which is receiving the yellow alarm

BPV

— a bipolar violation is a sequence of two or more consecutive pulses of the

same polarity

— if a T1 is designed to support B8ZS, but some portion of the facility is

configured for AMI in error, the AMI portion of the T1 may attempt to “fix”

the intentional bipolar violations used to represent 8 or more zeroes on a

B8ZS T1

— this may manifest as BPVs or BPVs with CRC-6 errors

— to verify that a T1 which is intended to be B8ZS is actually configured

properly, test the facility with a pattern of all zeroes

CSU reports no errors

but

DTE reports errors

— in some data applications using DSU functions, a condition is reported in

which the CSU does not report errors, but the customer Data Terminal

Equipment (DTE) does report errors

— this usually results from transmit data sampling errors at a DSU interface

at the opposite end of the circuit from the DTE reporting the errors

— if a CSU/DSU samples a zero when the DTE actually presented a one, the

transmitting CSU creates CRC checksum data based on the improperly

sampled bit(s), the data does not change on the T1 facility, and the receiving

CSU detects no error

— these types of errors are caused by a broken phase relationship between

the transmit clock provided by the DSU and the transmit data provided by

the DTE

— if errors of this type are reported, try changing the ST vs INV-ST selection

for DSU clocking in the DSU at the opposite end of the circuit

— for more information on DTE clocking issues, see the DIU 2130 User

Manual

Trouble

Suggestion