Dma status (dstat), Dma status, Dstat) – Avago Technologies LSI8751D User Manual

Page 139: Register: 0x0c (0x8c)

5-23

MSG

SMSG/ Status

2

C/D

SC_D/ Status

1

I/O

SI_O/ Status

0

This register returns the SCSI control line status. A bit is set when the

corresponding SCSI control line is asserted. These bits are not latched;

they are a true representation of what is on the SCSI bus at the time the

register is read. The resulting read data is synchronized before being

presented to the PCI bus to prevent parity errors from being passed to

the system. This register is used for diagnostics testing or operation in

low level mode.

Register: 0x0C (0x8C)

DMA Status (DSTAT)

Read Only

Reading this register clears any bits that are set at the time the register

is read, but does not necessarily clear the register because additional

interrupts are pending (the LSI53C875 stacks interrupts). The DIP bit in

the

register is also cleared. It is possible to mask

DMA interrupt conditions individually through the

register.

When performing consecutive 8-bit reads of the

,

SCSI Interrupt Status Zero (SIST0)

, and

registers (in any order), insert a delay equivalent to 12 CLK

periods between the reads to ensure that the interrupts clear properly.

See

Chapter 2, “Functional Description,”

for more information on

interrupts.

DFE

DMA FIFO Empty

7

This status bit is set when the DMA FIFO is empty. It is

possible to use it to determine if any data resides in the

FIFO when an error occurs and an interrupt is generated.

This bit is a pure status bit and does not cause an

interrupt.

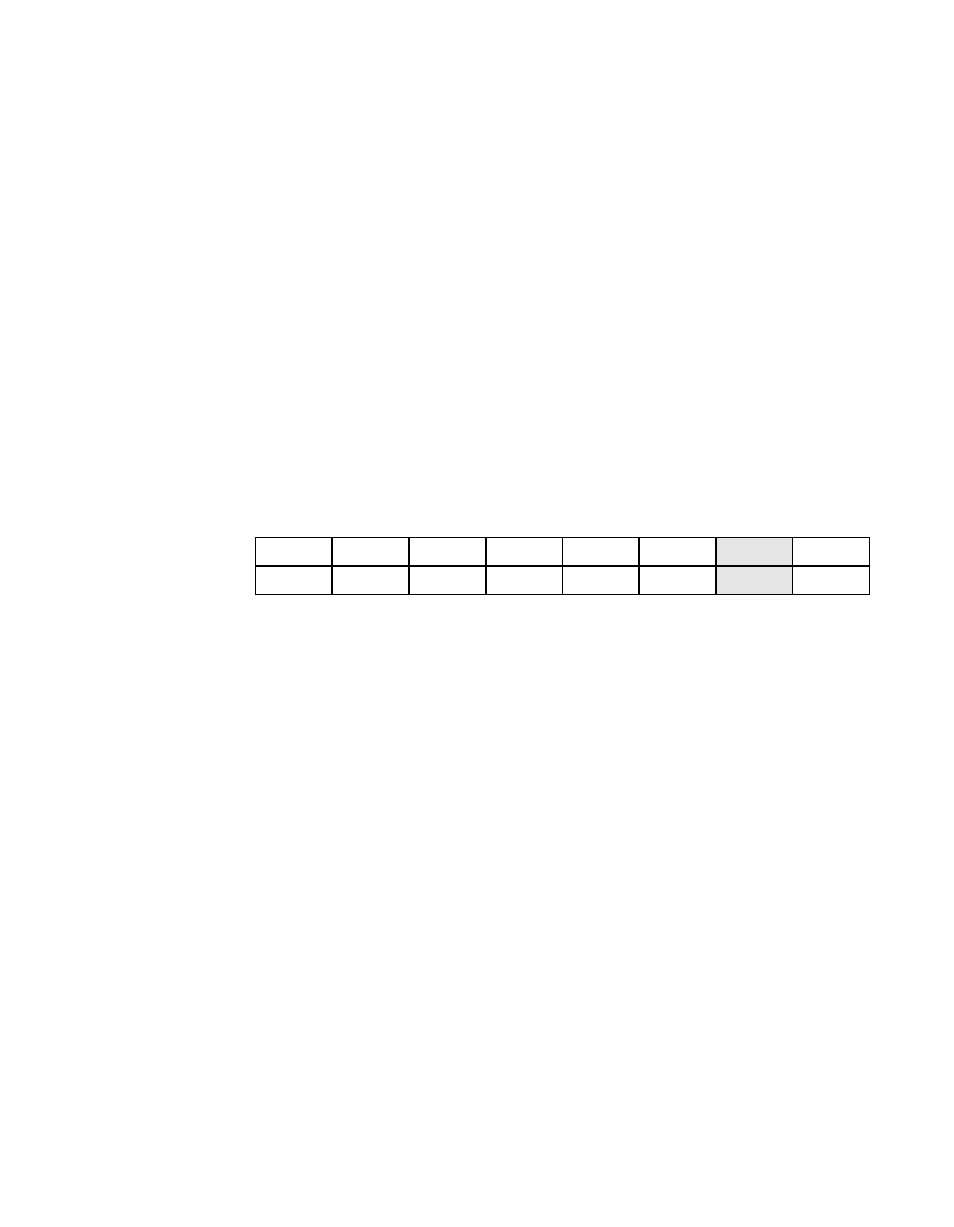

7

6

5

4

3

2

1

0

DFE

MDPE

BF

ABRT

SSI

SIR

R

IID

1

0

0

0

0

0

x

0