Avago Technologies LSI8751D User Manual

Page 273

Advertising

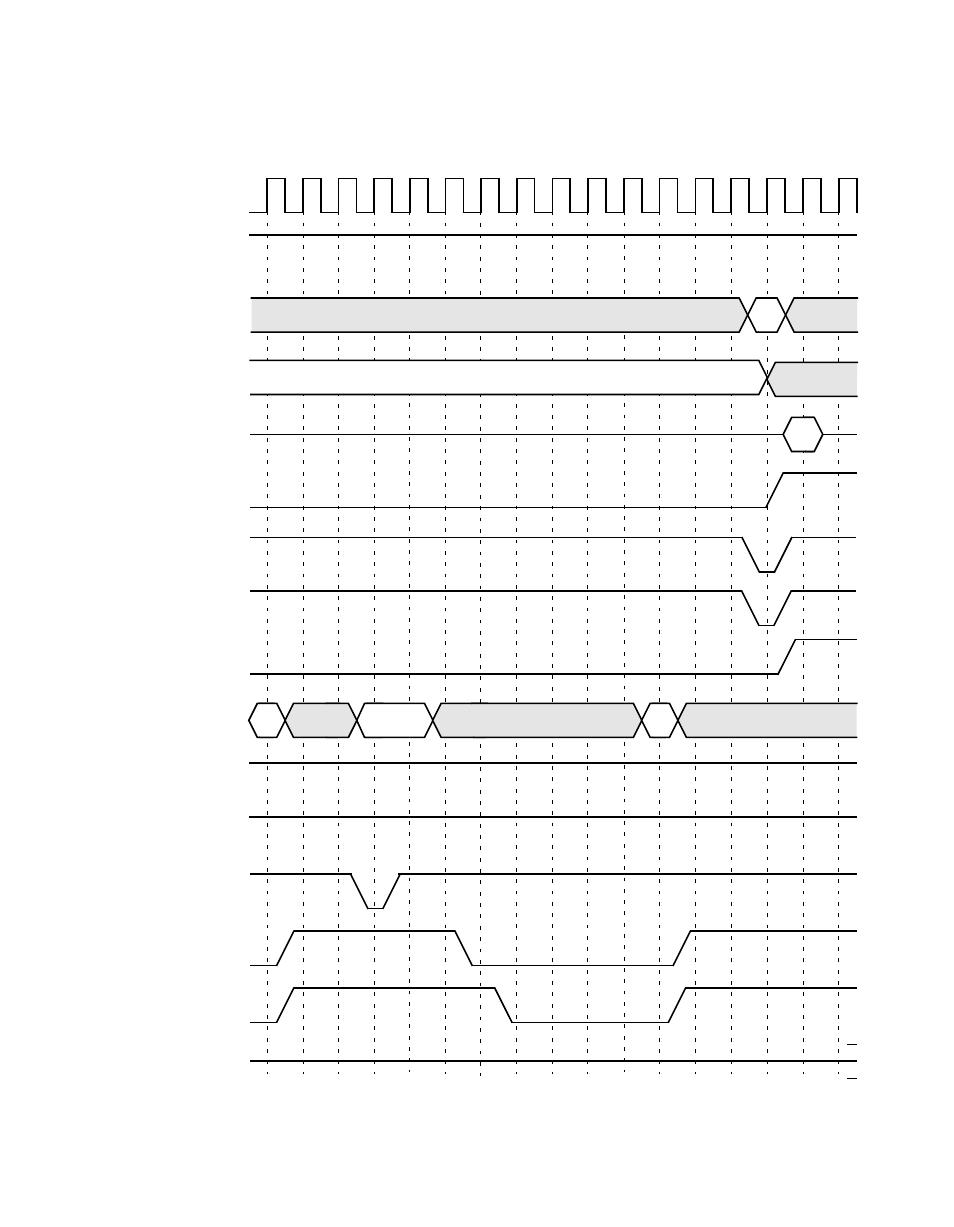

PCI and External Memory Interface Timing Diagrams

7-37

Figure 7.23 Read Cycle, Normal/Fast Memory (

≥

64 Kbyte), Multiple Byte Access

(Cont.)

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

CLK

(Driven by System)

FRAME/

(Driven by Master)

AD

(Driven by Master-Addr;

C_BE/

(Driven by Master)

LSI53C875-Data)

PAR

(Driven by Master-Addr;

LSI53C875-Data)

IRDY/

(Driven by Master)

TRDY/

(Driven by LSI53C875)

STOP/

(Driven by LSI53C875)

DEVSEL/

(Driven by LSI53C875)

MAD

(Addr driven by LSI53C875)

Data driven by memory)

GPIO2_MAS2/

(Driven by LSI53C875)

MAS1/

(Driven by LSI53C875)

MAS0/

(Driven by LSI53C875)

MOE/

(Driven by LSI53C875)

MCE/

(Driven by LSI53C875)

MWE/

(Driven by LSI53C875)

Out

Byte Enable

Low Order

Address

Data

In

33

Out

Data

Data

In

Advertising

This manual is related to the following products: