Altera SDI II MegaCore User Manual

Page 10

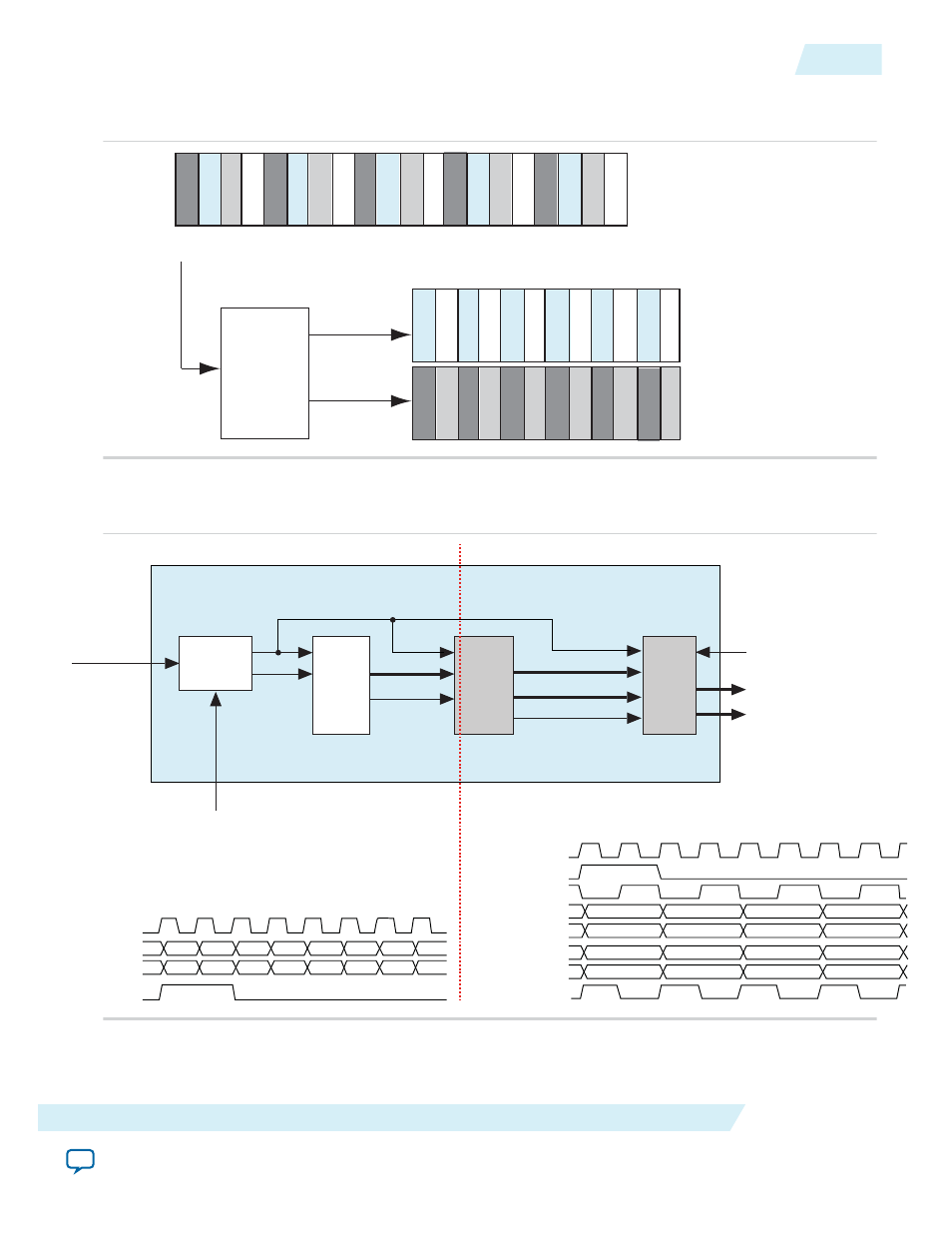

Figure 2-3: Example of 3G-SDI (Level B) to HD-SDI Dual Link Conversion

The figure shows the conversion of 3G-SDI (level B) data to two HD-SDI data streams.

3FF

h(

C2)

Demux

3FF

h(

C1)

3FF

h(

Y2)

3FF

h(

Y1)

000h(

C2)

000h(

C1)

000h(

Y2)

000h(

Y1)

XYZ(

C2)

XYZ(

C1)

XYZ(

Y2)

XYZ(

Y1)

LN0(

C2)

LN0(

C1)

LN0(

Y2)

LN0(

Y1)

LN1(

C2)

LN1(

C1)

LN1(

Y2)

LN1(

Y1)

3FF

h(

C1)

3FF

h(

Y1)

000h(

C1)

000h(

Y1)

XYZ(

C1)

XYZ(

Y1)

LN0(

C1)

LN0(

Y1)

LN1(

C1)

LN1(

Y1)

3FF

h(

C2)

3FF

h(

Y2)

000h(

C2)

000h(

Y2)

XYZ(

C2)

XYZ(

Y2)

LN0(

C2)

LN0(

Y2)

LN1(

C2)

LN1(

Y2)

000h(

C1)

000h(

Y1)

000h(

C2)

000h(

Y2)

3G-SDI Level B Interleaved Stream

Data Stream 1

HD-SDI Link A (10-bit)

HD-SDI Link B (10-bit)

Data Stream 2

Figure 2-4: Implementation of 3G-SDI (Level B) to HD-SDI Dual Link Conversion

The figure shows a block diagram of 3G-SDI (level B) to HD-SDI dual link conversion.

Transceiver

3-GB Signal

Protocol

3-GB

Demux

rxdata

rx_clkin_smpte372

(74.25 MHz or 74.175 MHz)

rx_dataout[19:0]

rdclk_3gb_div2 =

1H1L1H1L

xcvr_refclk (148.5 MHz or 148.35 MHz)

rx_clkout

(148.5 MHz or 148.35 MHz)

FIFO

rx_dataout_b[19:0]

rx_dataout[19:0]

rx_dataout_b[19:0]

wrreq

rxdata[19:0]

rx_trs

3-GB Receiver

rx_clkout

rx_trs

rxdata[19:10]

rxdata[9:0]

C1

C1

C1

C1

Y1

Y1

Y1

Y1

C2

C2

C2

C2

Y2

Y2

Y2

Y2

Y1

Y1

Y1

Y1

C1

C1

C1

C1

Y2

Y2

Y2

Y2

C2

C2

C2

C2

rx_clkin_smpte372

rx_dataout[19:10]

rx_dataout[9:0]

rx_clkdiv2

rx_dataout_b[19:10]

rx_dataout_b[9:0]

rx_clkout

rx_trs

UG-01125

2015.05.04

3G-SDI (Level B) to HD-SDI Dual Link Conversion

2-5

SDI II IP Core Overview

Altera Corporation