Transceiver, Transceiver -12 – Altera SDI II MegaCore User Manual

Page 54

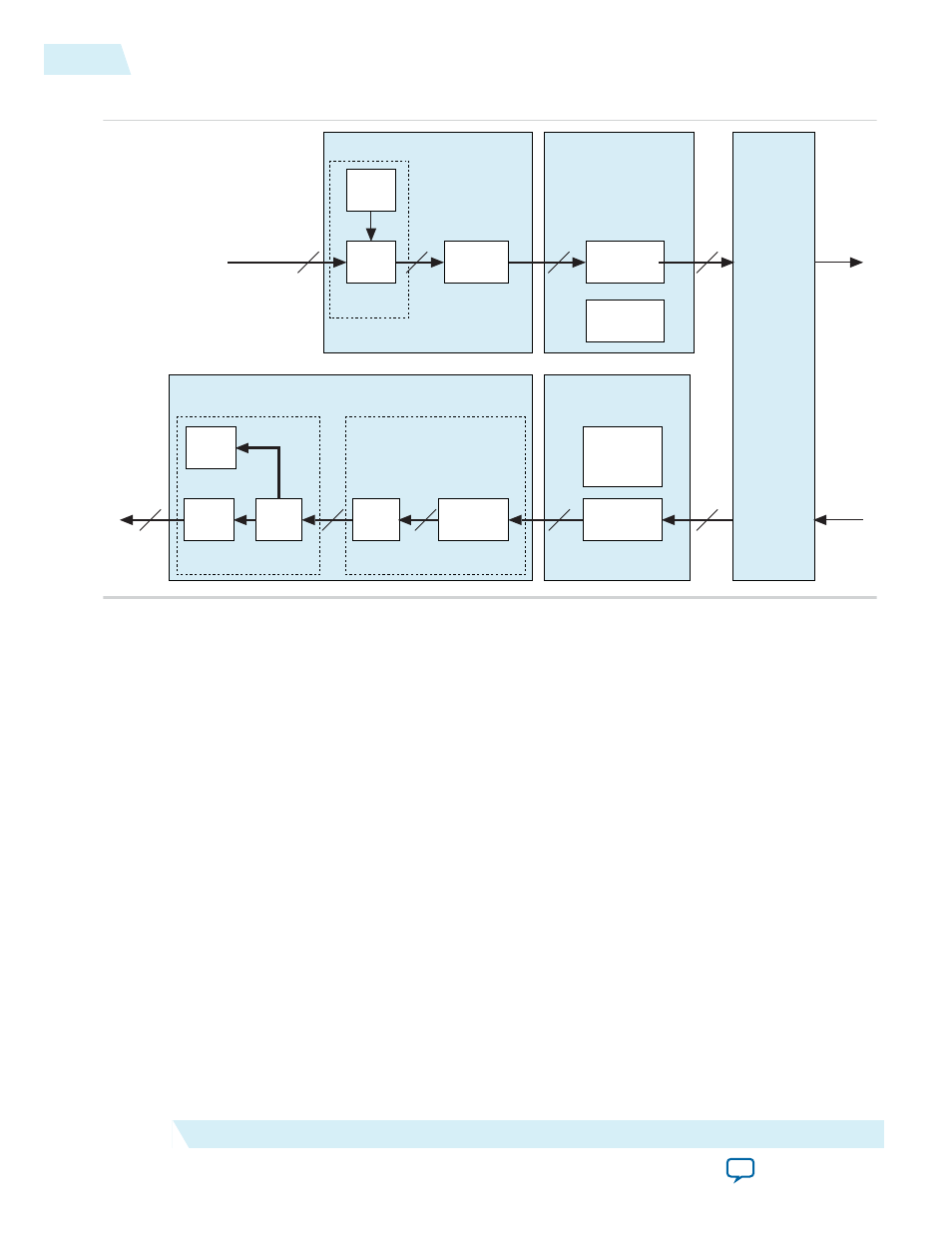

Figure 4-16: SD-SDI Duplex Mode Block Diagram

TX Protocol

Detect

Format

TRS

Aligner

Descrambler

RX

Oversample

Transceiver

Control

State Machine

Receive

Prealign

RX Protocol

RX PHY Management

& PHY Adapter

Parallel

Video Out

10

10

Match

TRS

10

Extract

Payload

ID

10

20

Match

TRS

Insert

Payload

ID

Scrambler

TX

Oversample

Generate

Clock Enable

Transmit

TX PHY Management

& PHY Adapter

Transceiver

Parallel Video In

10

SDI Out

10

10

20

SDI In

Transceiver

The transceiver block consists of two components—PHY management & adapter and hard transceiver.

These two components handle the serial transport aspects of the SDI.

Note: The transceiver block is only available for Arria V, Cyclone V, and Stratix V devices. For Arria 10

devices, you must generate the transceiver and the TX PLL separately.

The hard transceiver uses the Altera Native PHY IP Core for the following devices:

• Arria V GX (altera_xcvr_native_av_hw.tcl)

• Arria V GZ (altera_xcvr_native_avgz_hw.tcl)

• Stratix V (altera_xcvr_native_sv_hw.tcl)

• Cyclone V (altera_xcvr_native_cv_hw.tcl)

The SDI II IP core instantiates the PHY IP core using the Tcl file associated with each device.

The block diagram below illustrates the Native PHY IP core setup in the SDI II IP core (duplex) data path.

4-12

Transceiver

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description