Smpte rp168 switching support, Sd 20-bit interface for dual/triple standard, Smpte rp168 switching support -6 – Altera SDI II MegaCore User Manual

Page 11: Sd 20-bit interface for dual/triple standard -6

SMPTE RP168 Switching Support

The SMPTE RP168 standard defines the requirements for synchronous switching between two video

sources to take place with minimal interference to the receiver. The RP168 standard has restrictions for

which lines the source switching can occur.

The SDI II IP core has flexibility and does not restrict you to switch at only a particular line defined in the

RP168 standard. You can perform switching at any time between different video sources as long as the

source has similar standard and format. After switching, all the status output signals, including the

rx_trs_locked

,

rx_frame_locked

, and

rx_align_locked

signals, remain unchanged. You should

should not see any interrupts at downstream.

SD 20-Bit Interface for Dual/Triple Standard

For a common SD interface, the serial data format is 10 bits wide, whereas for HD or 3G, the data format

is 20 bits wide, divided into two parallel 10-bit datastreams (known as Y and C).

To make the interface bit width common for all standards in the dual standard or triple standard SDI

mode:

• The receiver can extract the data and align them in 20-bit width

• The transmitter can accept SD data in 20-bit width and retransmit them successfully

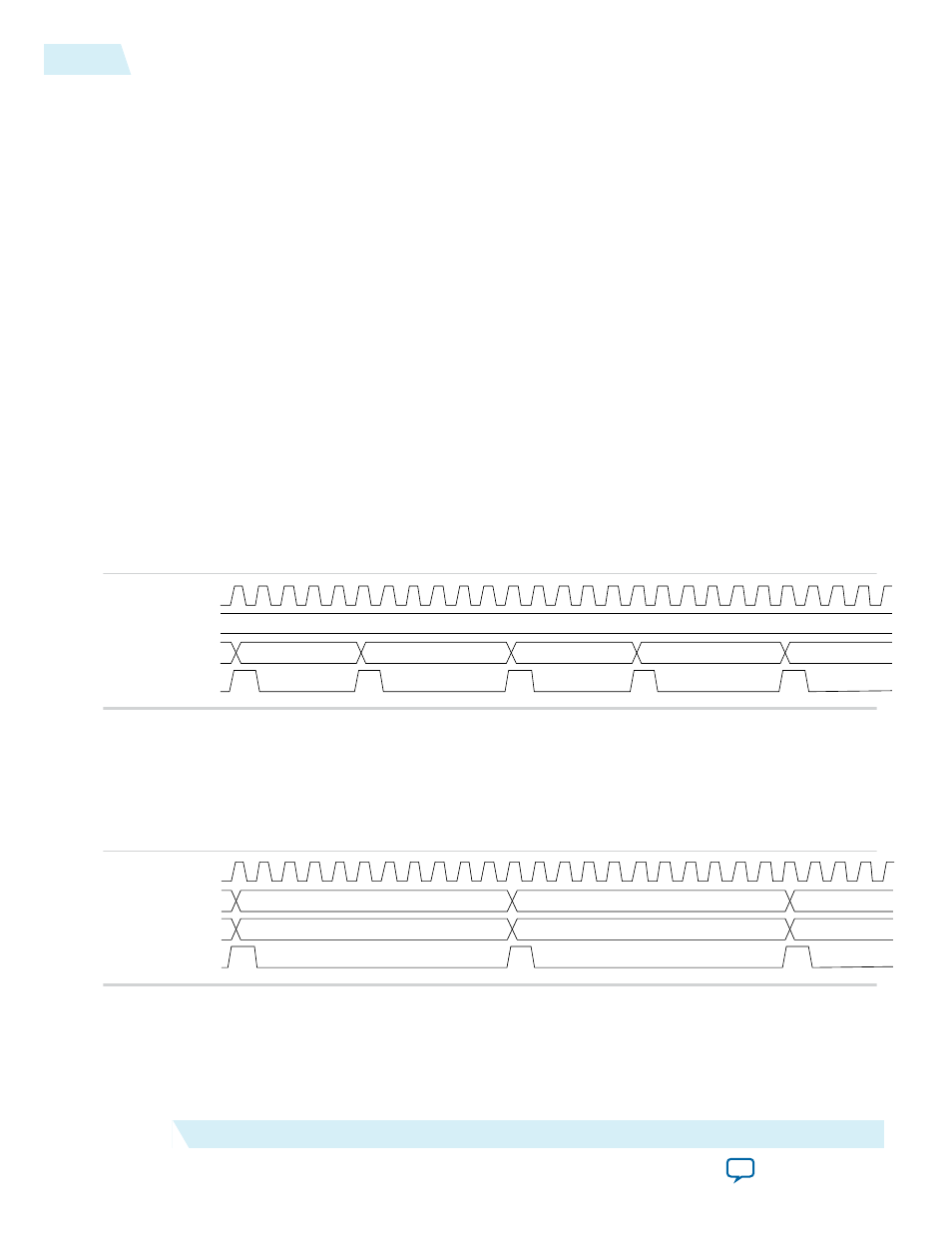

The timing diagrams below show a comparison of data arrangement between 10-bit and 20-bit interface.

Figure 2-5: SD 10-Bit Interface

rx_clkout(148.5 MHz)

rx_dataout[19:10]

rx_dataout[9:0]

rx_dataout_valid

Don’t Care

Cb

Y

Cr

Y

Cb

• The upper 10 bits of

rx_dataout

are insignificant data.

• The lower 10 bits of

rx_dataout

are Luma (Y) and chroma (Cb, Cr) channels (interleaved).

• The 1H 4L 1H 5L cadence of

rx_dataout_valid

repeats indefinitely (ideal).

Figure 2-6: SD 20-Bit Interface

rx_clkout(148.5 MHz)

rx_dataout[19:10]

rx_dataout[9:0]

rx_dataout_valid

Cb

Y

Cr

Y

Y

Cb

• The upper 10 bits of

rx_dataout

are Luma (Y) channel and the lower 10 bits are Chroma (Cb, Cr)

channel.

• The 1H 10L cadence of

rx_dataout_valid

repeats indefinitely (ideal).

2-6

SMPTE RP168 Switching Support

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Overview