Tx sample, Clock enable generator, Tx sample -18 – Altera SDI II MegaCore User Manual

Page 60: Clock enable generator -18

TX Sample

The TX sample submodule is a transmit oversampling block. It repeats each bit of the input word a given

number of times and constructs the output words.

This submodule relies on the fact that the input data is only valid on 1/x of the clock cycles, where x is the

oversampling factor. Both the input and output words are clocked from the same clock domain.

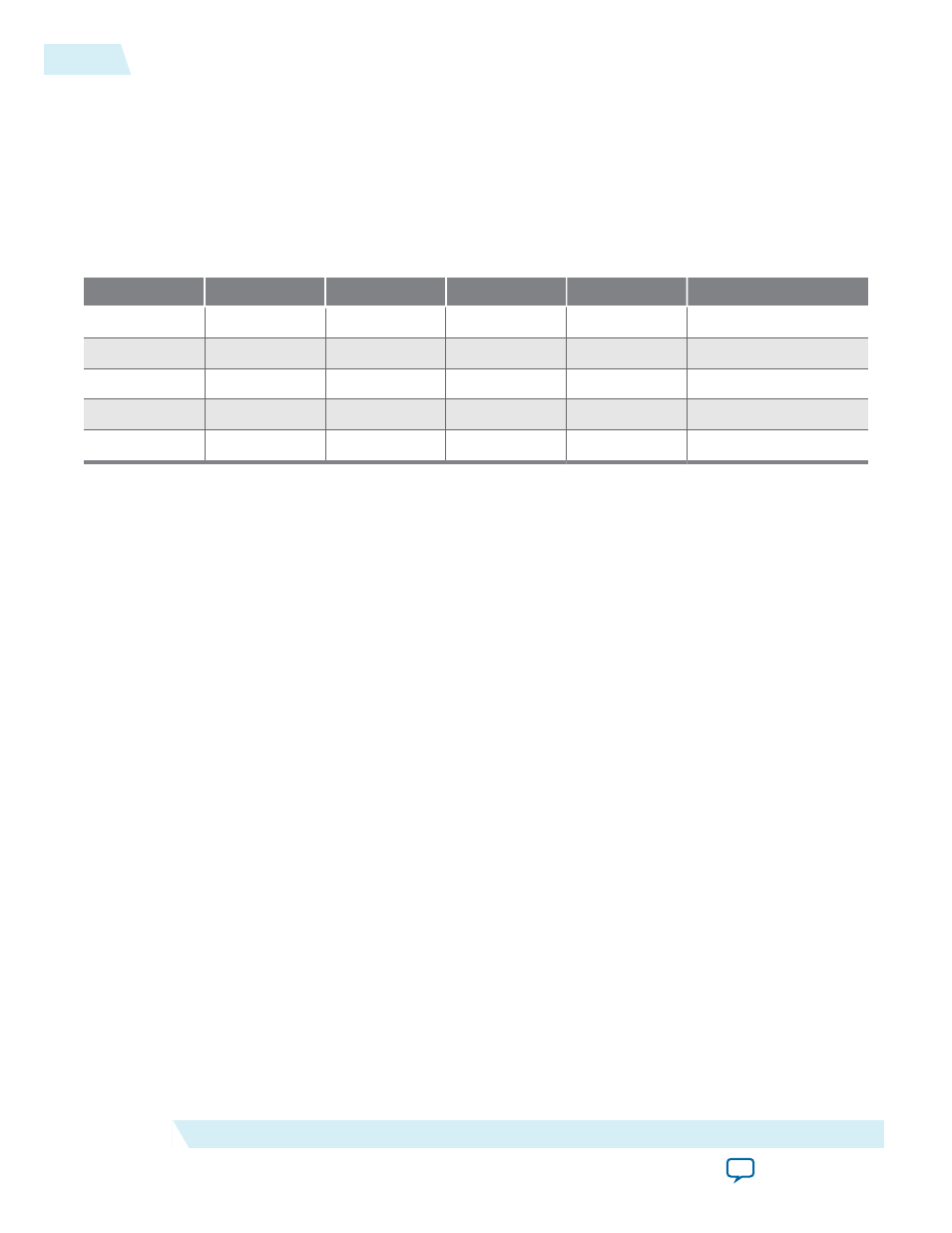

Table 4-2: Oversampling Requirement

The table below lists the number of times oversampling is required for the different video standards.

SD-SDI

SD-SDI

HD-SDI

Dual Rate

Triple Rate

Multi Rate

SD-SDI

11

11

11

11

44

HD-SDI

—

2

2

2

8

3G-SDI

—

—

—

—

4

6G-SDI

—

—

—

—

2

12G-SDI

—

—

—

—

—

Clock Enable Generator

The clock enable generator is a simple logic that generates a clock enable signal.

The clock enable signal serves as a data valid signal,

tx_datain_valid

for the incoming video data signal,

tx_datain

. The video data signal is based on the incoming video standard signal,

tx_std

. The transmit

parallel clock,

tx_pclk

, can be a single frequency of either 148.5 MHz or 148.35 MHz.

The clock enable generator generates a clock signal in the following conditions:

• If the

tx_datain

signal is SD—generate a

tx_datain_valid

pulse every 5th and 11th clock cycle of

the tx_pclk domain.

• If the

tx_datain

signal is HD—generate a

tx_datain_valid

pulse every other clock cycle of the

tx_pclk domain.

• If the

tx_datain

signal is neither SD nor HD—the

tx_datain_valid

pulse remains high for 3G, 6G,

or 12G.

4-18

TX Sample

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description