Altera SDI II MegaCore User Manual

Page 22

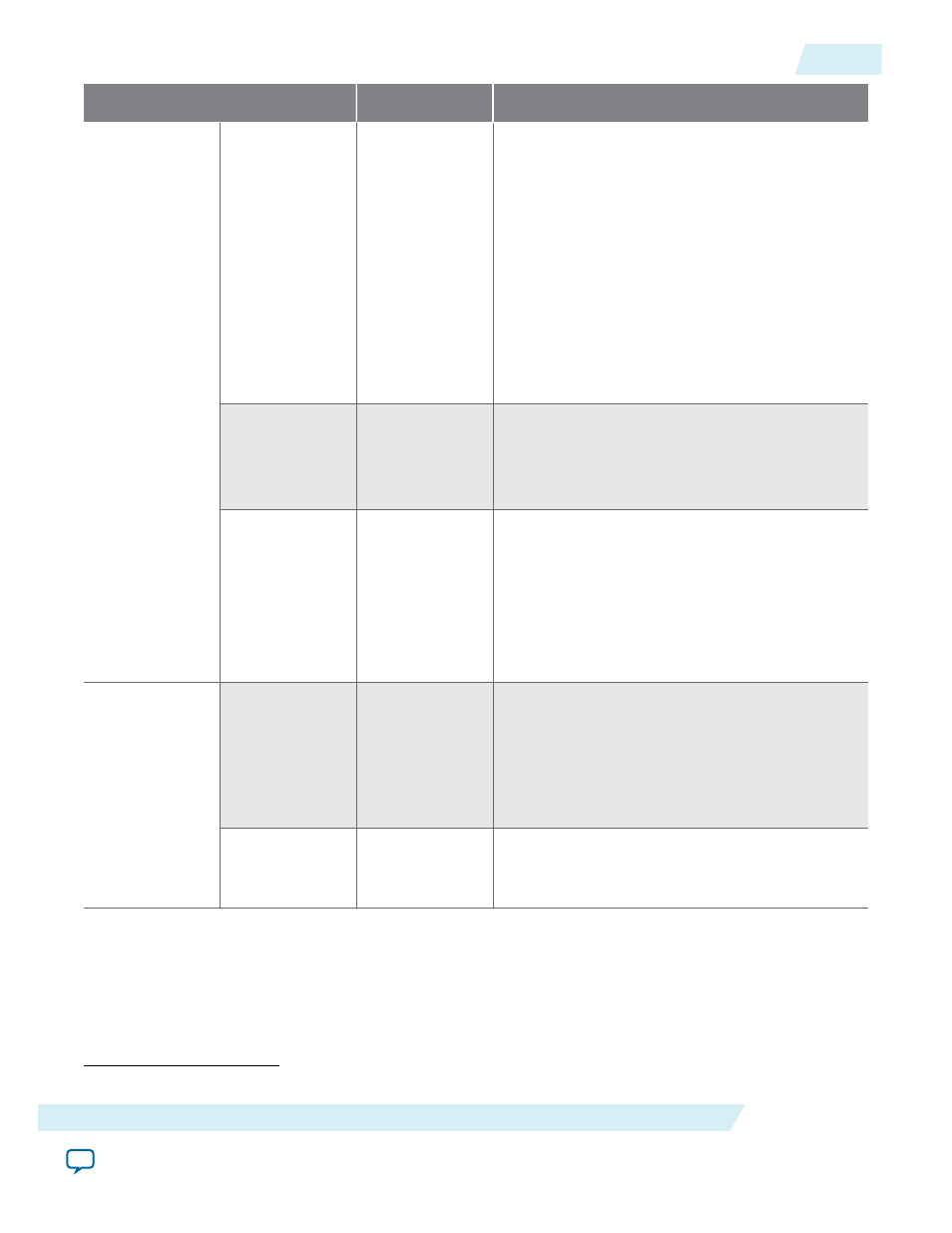

Parameter

Value

Description

Transceiver

Options

(2)

Dynamic Tx clock

switching

Off, Tx PLLs

switching, Tx PLL

reference clocks

switching

• Off: Disable dynamic switching

• Tx PLLs switching: Instantiates two PLLs,

each with a reference input clock

• Tx PLL reference clocks switching: Instanti‐

ates a PLL with two reference input clocks.

Note: This option is not available if you

select ATX PLL.

Turn on this option to allow dynamic switching

between 1 and 1/1.001 data rates.

Note: This option is only available for TX or

bidirectional ports, and all video

standards except SD-SDI.

Transceiver

reference clock

frequency

148.5/148.35

MHz,

74.25/74.175

MHz,

Selects the transceiver reference clock frequency.

The 74.25/74.175 MHz option is available only

for HD-SDI and HD-SDI dual link video

standards, and if you select CMU as the TX PLL.

TX PLL type

CMU, ATX

Selects the transmitter PLL for TX or bidirec‐

tional ports.

ATX PLL is useful for bidirectional channels—

you can use the ATX PLL as the transmitter PLL

instead of the CMU PLL from another channel.

ATX PLL is only available in the Stratix V and

Arria V GZ families

Receiver

Options

Increase error

tolerance level

On, Off

• On: Error tolerance level = 15

• Off: Error tolerance level = 4

Turn on this option to increase the error

tolerance level for consecutive missed end of

active videos (EAVs), start of active videos

(SAVs), or erroneous frames.

CRC error output On, Off

• On: CRC monitoring (Not applicable for SD-

SDI mode)

• Off: No CRC monitoring (saves logic)

(2)

These options are available only for Arria V, Cyclone V, and Stratix V devices.

UG-01125

2015.05.04

SDI II IP Core Parameters

3-7

SDI II IP Core Getting Started

Altera Corporation