Altera SDI II MegaCore User Manual

Page 80

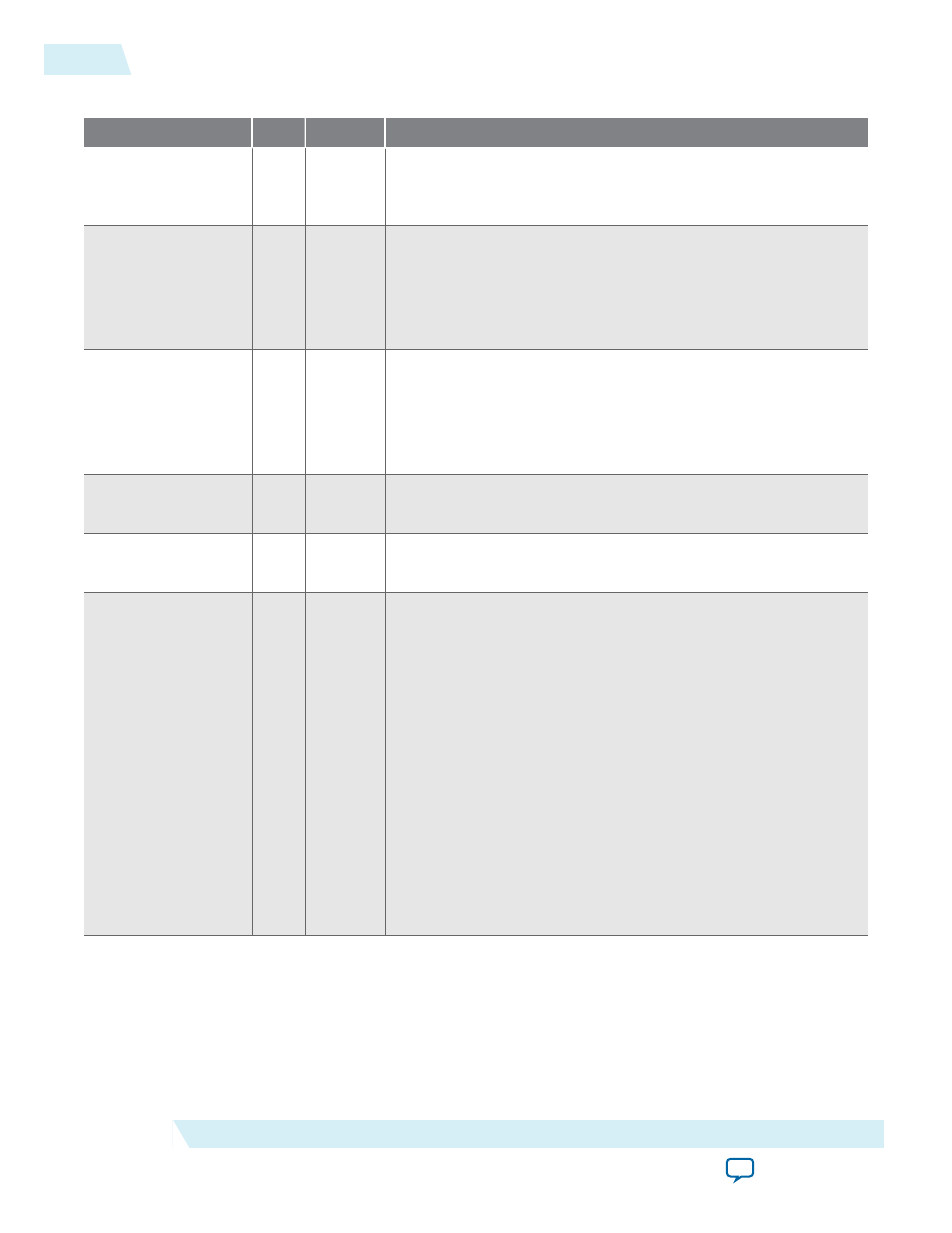

Table 4-7: Transceiver (PHY Management, PHY Adapter, and Hard Transceiver) Signals

Signal

Width Direction

Description

rx_rst

1

Input

Reset signal for the receiver. This signal is active high and level

sensitive. This reset signal must be synchronous to the

rx_

coreclk

or

rx_coreclk_hd

clock domain.

rx_coreclk

1

Input

148.5-MHz or 148.35-MHz receiver controller clock input. The

frequency of this signal must be similar to the frequency of the

xcvr_refclk

signal. Not applicable for HD-SDI and HD-SDI

dual link modes.

Note: Not applicable for Arria 10 devices.

rx_coreclk_hd

1

Input

74.25-MHz or 74.175-MHz receiver controller clock input. The

frequency of this signal must be similar to the frequency of the

xcvr_refclk

signal. Applicable for HD-SDI and HD-SDI dual

link modes only.

Note: Not applicable for Arria 10 devices.

tx_coreclk

1

Input

148.5-MHz or 148.35-MHz transmitter clock input signal. Not

applicable for HD-SDI and HD-SDI dual link modes.

tx_coreclk_hd

1

Input

74.25-MHz or 74.175-MHz transmitter clock input signal.

Applicable for HD-SDI and HD-SDI dual link modes only.

xcvr_refclk

1

Input

Clock input for the hard transceiver. Only a single reference

clock frequency is required for the receiver to support both 1 and

1/1.001 rate.

For example, a clock frequency of 148.5 MHz for the triple

standard receiver can receive both 2.97 Gbps and 2.967 Gbps

video stream. But a clock frequency of 148.5 MHz and

148.35 MHz are required to transmit 2.97 Gbps and 2.967 Gbps

video stream, respectively.

• SD-SDI = 148.5 MHz or 148.35 MHz

• HD-SDI = 74.25 MHz or 74.175 MHz

• 3G-SDI = 148.5 MHz or 148.35 MHz

• HD-SDI Dual Link: 74.25 MHz or 74.175 MHz

• Dual Standard: 148.5 MHz or 148.35 MHz

• Triple Standard: 148.5 MHz or 148.35 MHz

Note: Not applicable for Arria 10 devices.

4-38

SDI II IP Core Signals

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description