Design example components – Altera SDI II MegaCore User Manual

Page 29

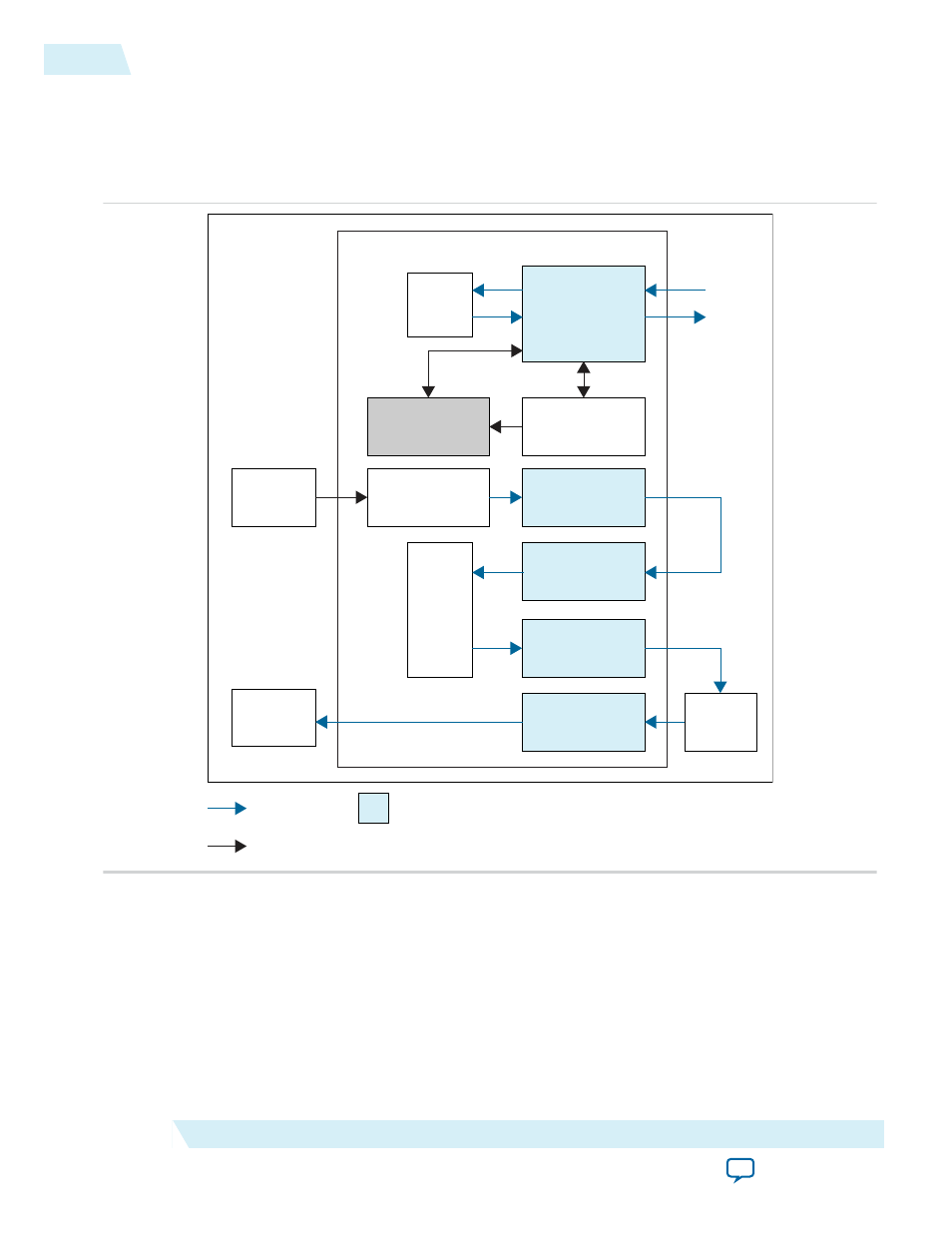

Figure 3-4: Design Example Entity and Simulation Testbench for 3G-SDI (Level B) to HD-SDI Dual Link

Conversion

The figure below illustrates the generated design example entity and simulation testbench when you

generate 3G-SDI or triple rate SDI receiver with Convert 3G-SDI (level B) to HD-SDI dual link option

enabled.

Loopback

Path

Ch0

Loopback

(SDI Duplex)

Reconfiguration

Management/Router

Ch1 Test

(3-Gb SDI TX)

Ch1 DUT

(3-Gb SDI RX)

B to A

Video Pattern

Generator

Test

Control

Ch2 Test

(HD DL SDI TX)

Ch2 Test

(HD DL SDI RX)

TX

Checker

RX

Checker

Loopback

Path

Data

Control

SDI II IP Core

Design Example

Testbench

Transceiver

Reconfiguration

Controller

Design Example Components

The Arria V, Cyclone V, and Stratix V design examples for the SDI II IP core consist of the following

components:

• Video pattern generator

• Transceiver reconfiguration controller

• Reconfiguration management

• Reconfiguration router

3-14

Design Example Components

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Getting Started