Transceiver reconfiguration controller signals, Transceiver reconfiguration controller signals -23 – Altera SDI II MegaCore User Manual

Page 38

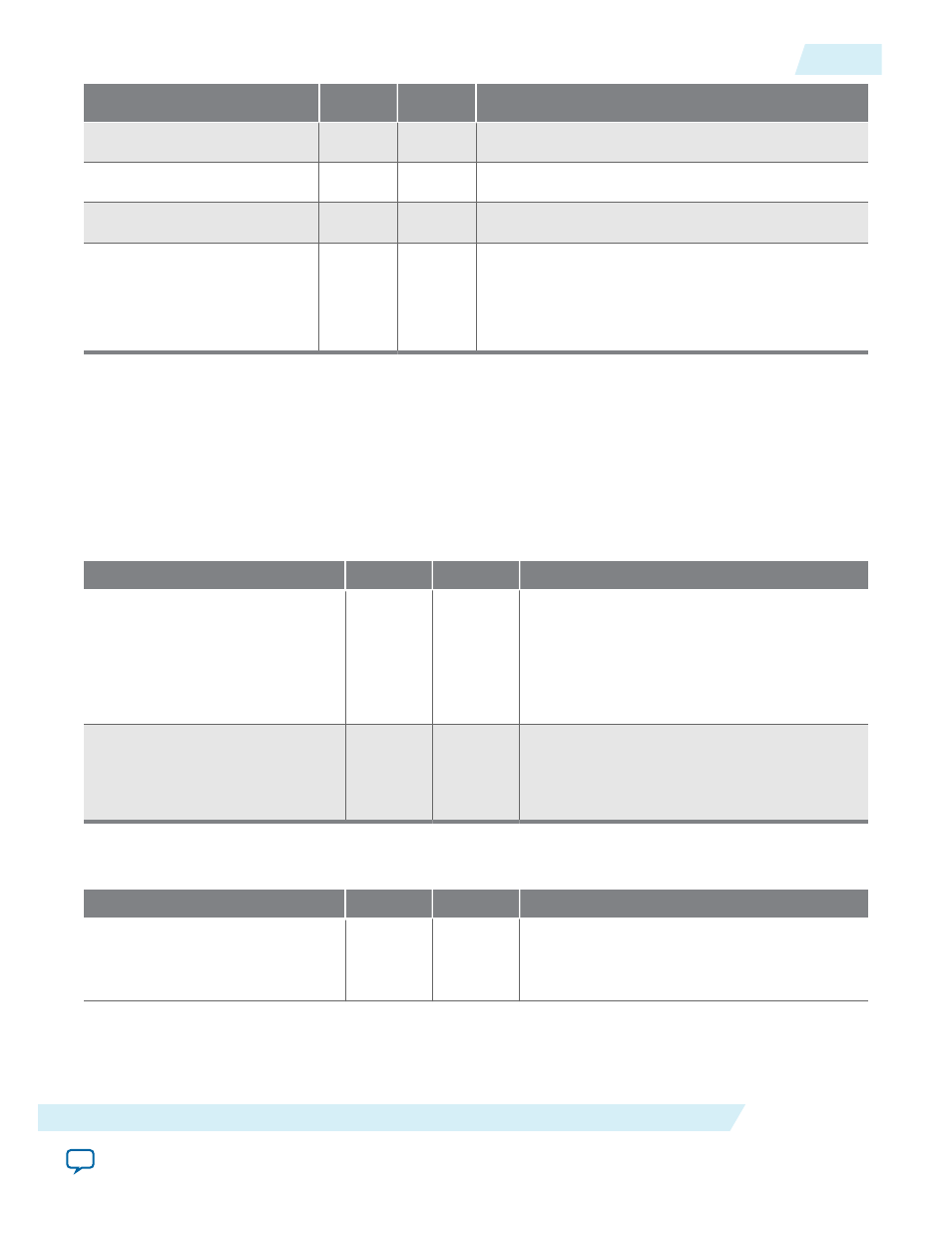

Signal

Width

Direction

Description

pattgen_patho

1

Input

Set to 1 to generate pathological pattern.

pattgen_blank

1

Input

Set to 1 to generate black signal.

pattgen_no_color

1

Input

Set to 1 to generate bars with no color.

pattgen_sgmt_frame

1

Input

Set to 1 to generate segmented frame picture for

tx_

format

:

• 0100: SMPTE274M 1080sF30

• 0101: SMPTE274M 1080sF25

Related Information

Transceiver Reconfiguration Controller Signals

Table 3-9: Transceiver Reconfiguration Controller Signals for Arria V, Cyclone V, and Stratix V Devices

Table below lists the input signals for the transceiver reconfiguration controller. The listed signals are exported at

the top level of the design example. Other signals—that are not exported—connects within the design example

entity.

Signal

Width

Direction

Description

reconfig_clk

1

Input

Clock signal for the transceiver reconfigura‐

tion controller and reconfiguration

management/router. Refer to the transceiver

reconfiguration controller section in the

Altera Transceiver PHY IP User Guide for

information about the frequency range.

reconfig_rst

1

Input

Reset signal for the transceiver reconfigura‐

tion controller and reconfiguration

management/router. This signal is active high

and level sensitive.

Table 3-10: Transceiver Reconfiguration Controller Signals for Arria 10 Devices

The table below describes the signals available for the reconfiguration controller.

Signal

Width

Direction

Description

xcvr_reconfig_clk

1

Input

Clock signal for reconfiguration user logic.

This clock must share the same clock source

as

reconfig_clk

in the transceiver.

UG-01125

2015.05.04

Transceiver Reconfiguration Controller Signals

3-23

SDI II IP Core Getting Started

Altera Corporation