Altera Arria V GZ Avalon-ST User Manual

Page 120

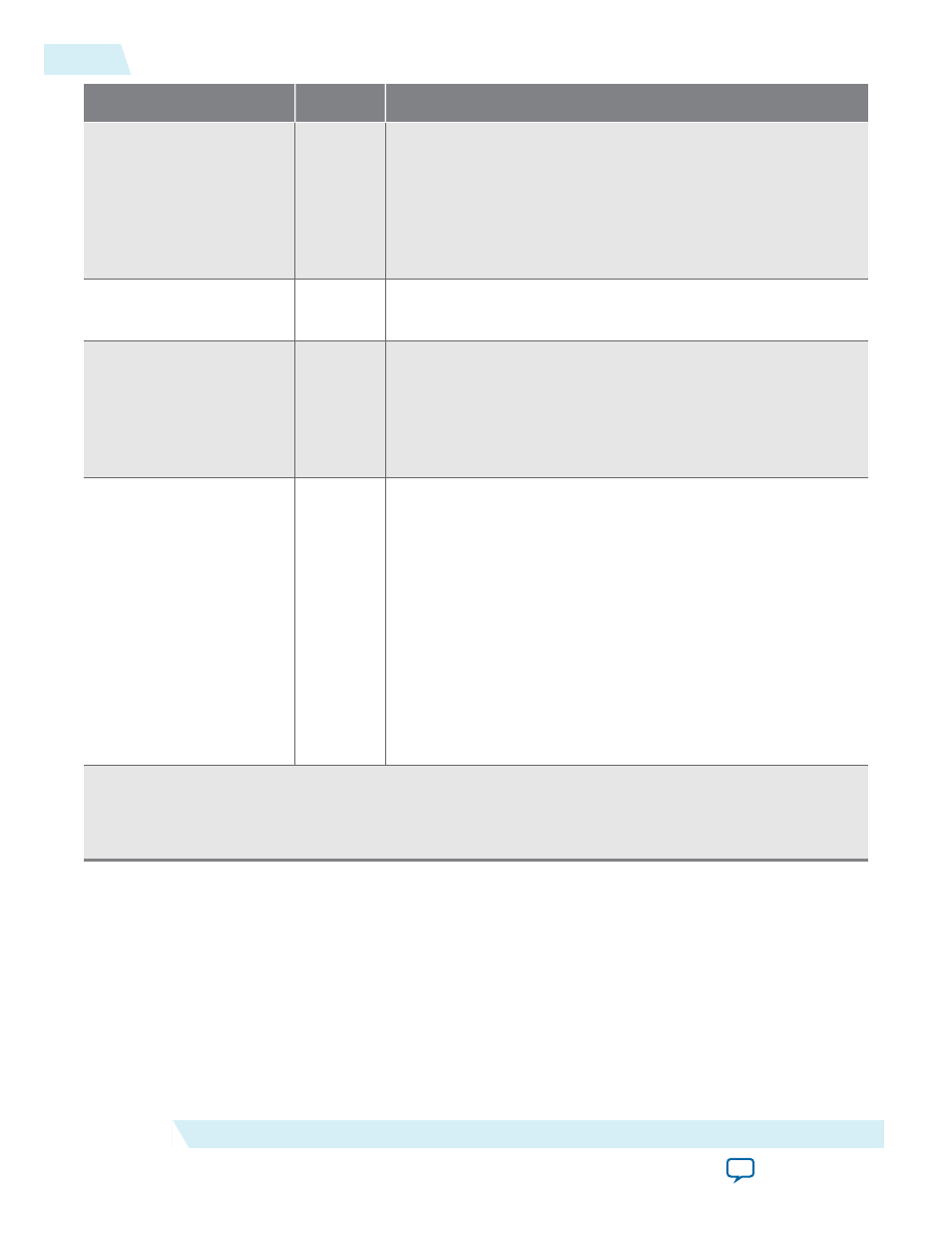

Signal

Direction

Description

• 5’b11010: Speed.Recovery

• 5’b11011: Recovery.Equalization, Phase 0

• 5’b11100: Recovery.Equalization, Phase 1

• 5’b11101: Recovery.Equalization, Phase 2

• 5’b11110: Recovery.Equalization, Phase 3

• 5’b11111: Recovery.Equalization, Done

rxfreqlocked0

(1)

Input

When asserted indicates that the

pclk_in

used for PIPE

simulation is valid.

rxdataskip0

Output

For Gen3 operation. Allows the PCS to instruct the RX interface

to ignore the RX data interface for one clock cycle. The following

encodings are defined:

• 1’b0: RX data is invalid

• 1’b1: RX data is valid

eidleinfersel0[2:0]

Output

Electrical idle entry inference mechanism selection. The

following encodings are defined:

• 3'b0xx: Electrical Idle Inference not required in current

LTSSM state

• 3'b100: Absence of COM/SKP Ordered Set in the 128 us

window for Gen1 or Gen2

• 3'b101: Absence of TS1/TS2 Ordered Set in a 1280 UI interval

for Gen1 or Gen2

• 3'b110: Absence of Electrical Idle Exit in 2000 UI interval for

Gen1 and 16000 UI interval for Gen2

• 3'b111: Absence of Electrical idle exit in 128 us window for

Gen1

Notes:

1. These signals are for simulation only. For Quartus II software compilation, these pipe signals can be

left floating.

5-68

PIPE Interface Signals

UG-01127_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions