Altera Arria V GZ Avalon-ST User Manual

Page 41

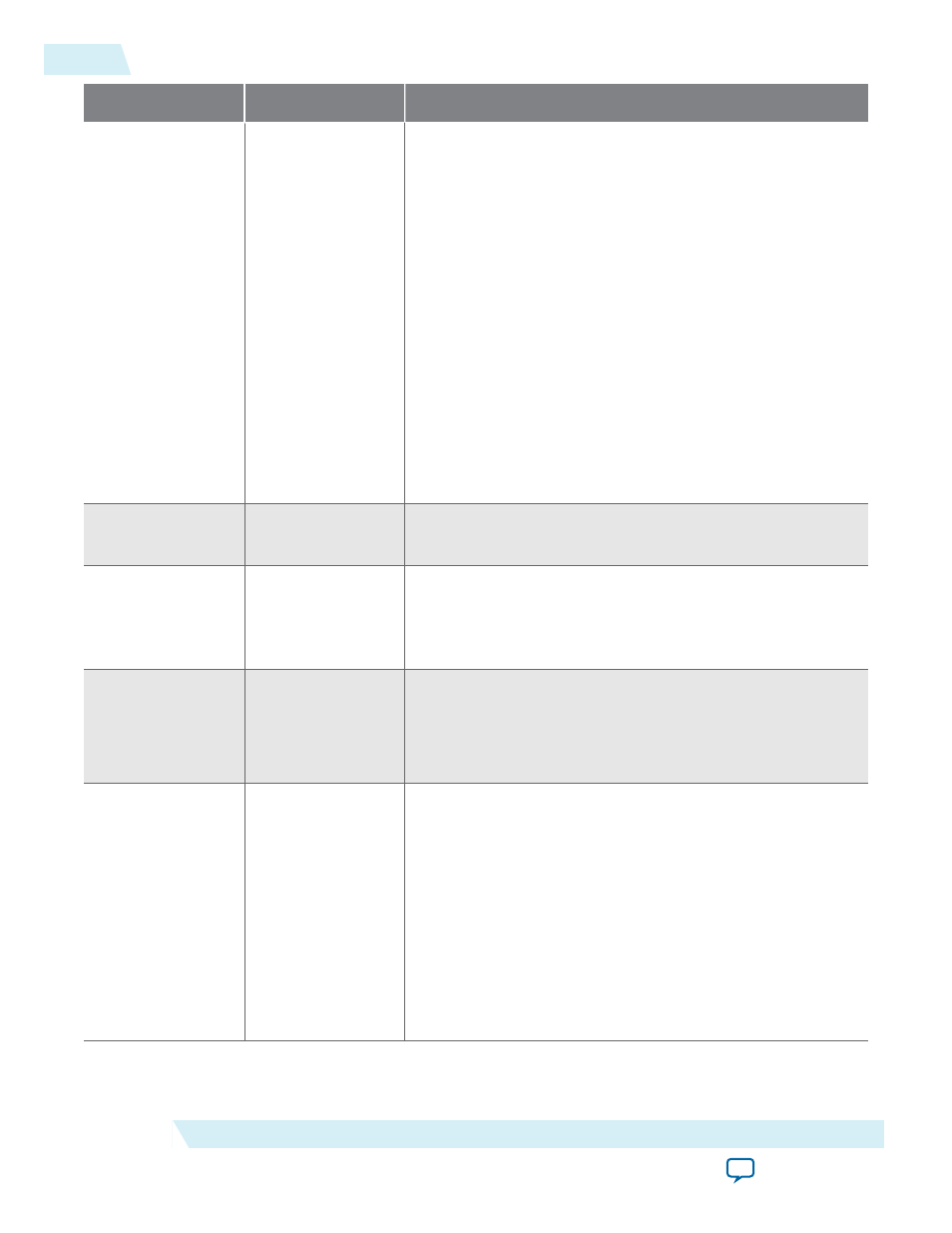

Parameter

Value

Description

Reference clock

frequency

100 MHz

125 MHz

The PCI Express Base Specification 3.0 requires a

100 MHz ±300 ppm reference clock. The 125 MHz reference

clock is provided as a convenience for systems that include a

125 MHz clock source. For more information about Gen3

operation, refer to 4.3.8 Refclk Specifications for 8.0 GT/sin the

specification.

For Gen3, Altera recommends using a common reference

clock (0 ppm) because when using separate reference clocks

(non 0 ppm), the PCS occasionally must insert SKP symbols,

potentially causes the PCIe link to go to recovery. Arria V GZ

PCIe Hard IP in Gen1 or Gen2 modes are not affected by this

issue. Systems using the common reference clock (0 ppm) are

not affected by this issue. The primary repercussion of this is a

slight decrease in bandwidth. On Gen3 x8 systems, this

bandwidth impact is negligible. If non 0 ppm mode is

required, so that separate reference clocks are being used,

please contact Altera for further information and guidance.

Use 62.5 MHz

application clock

On/Off

This mode is only available only for Gen1 ×1.

Use deprecated

RX Avalon-ST

data byte enable

port (rx_st_be)

On/Off

This parameter is only available for the Avalon-ST Arria V GZ

Hard IP for PCI Express.

Enable byte

parity ports on

Avalon-ST

interface

On/Off

When On, the RX and TX datapaths are parity protected.

Parity is odd.

This parameter is only available for the Avalon-ST Arria V GZ

Hard IP for PCI Express.

Enable multiple

packets per cycle

On/Off

When On, the 256-bit Avalon-ST interface supports the

transmission of TLPs starting at any 128-bit address

boundary, allowing support for multiple packets in a single

cycle. To support multiple packets per cycle, the Avalon-ST

interface includes 2 start of packet and end of packet signals

for the 256-bit Avalon-ST interfaces. This feature is only

supported for Gen3 ×8.

For more information refer to

Enabling Multiple Packets per Cycle

on page 5-17 and

Multiple Packets per Cycle on the Avalon-ST TX 256-Bit

4-4

System Settings

UG-01127_avst

2014.08.18

Altera Corporation

Parameter Settings