Understanding simulation log file generation, Simulating the example design – Altera Arria V GZ Avalon-ST User Manual

Page 29

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file,

altpcie_

monitor_<dev>_dlhip_tlp_file_log.log

in your simulation directory.

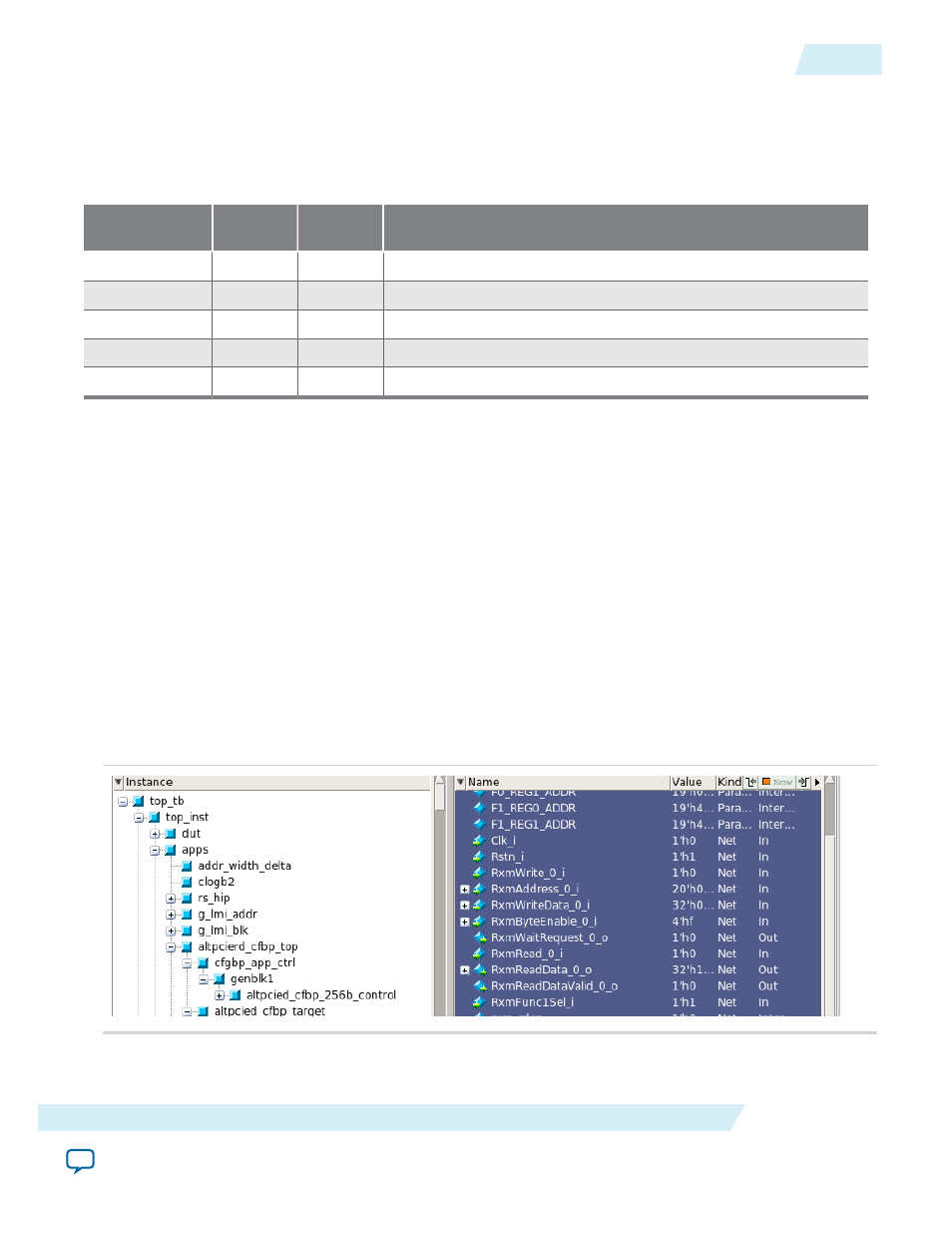

Table 3-3: Sample Simulation Log File Entries

Time

TLP Type

Payload

(Bytes)

TLP Header

17989 RX

CfgRd0

0004

04000001_0000000F_01080008

17989 RX

MRd

0000

00000000_00000000_01080000

18021 RX

CfgRd0

0004

04000001_0000010F_0108002C

18053 RX

CfgRd0

0004

04000001_0000030F_0108003C

18085 RX

MRd

0000

00000000_00000000_0108000C

Simulating the Example Design

Follow these steps to simulate the Qsys system using ModelSim:

1. In a terminal window, change to the

<working_dir>/top/testbench/mentor

directory.

2. Start the ModelSim simulator by typing

vsim

.

3. To compile the simulation, type the following commands in the terminal window:

•

source msim_setup.tcl

(The

msim_setup.tcl

file defines aliases.

•

ld_debug

(The

ld_debug

command argument stops optimizations, improving visibility in the

ModelSim waveforms. )

The following figure shows the design hierarchy for the Configuration Space Bypass Example Design after

compilation.

Figure 3-3: Design Hierarchy for the Configuration Space Bypass Example Design for 256-Bit Avalon-ST

Interface

UG-01127_avst

2014.08.18

Understanding Simulation Log File Generation

3-5

Getting Started with the Configuration Space Bypass Mode Qsys Example Design

Altera Corporation