Pld_clk – Altera Arria V GZ Avalon-ST User Manual

Page 144

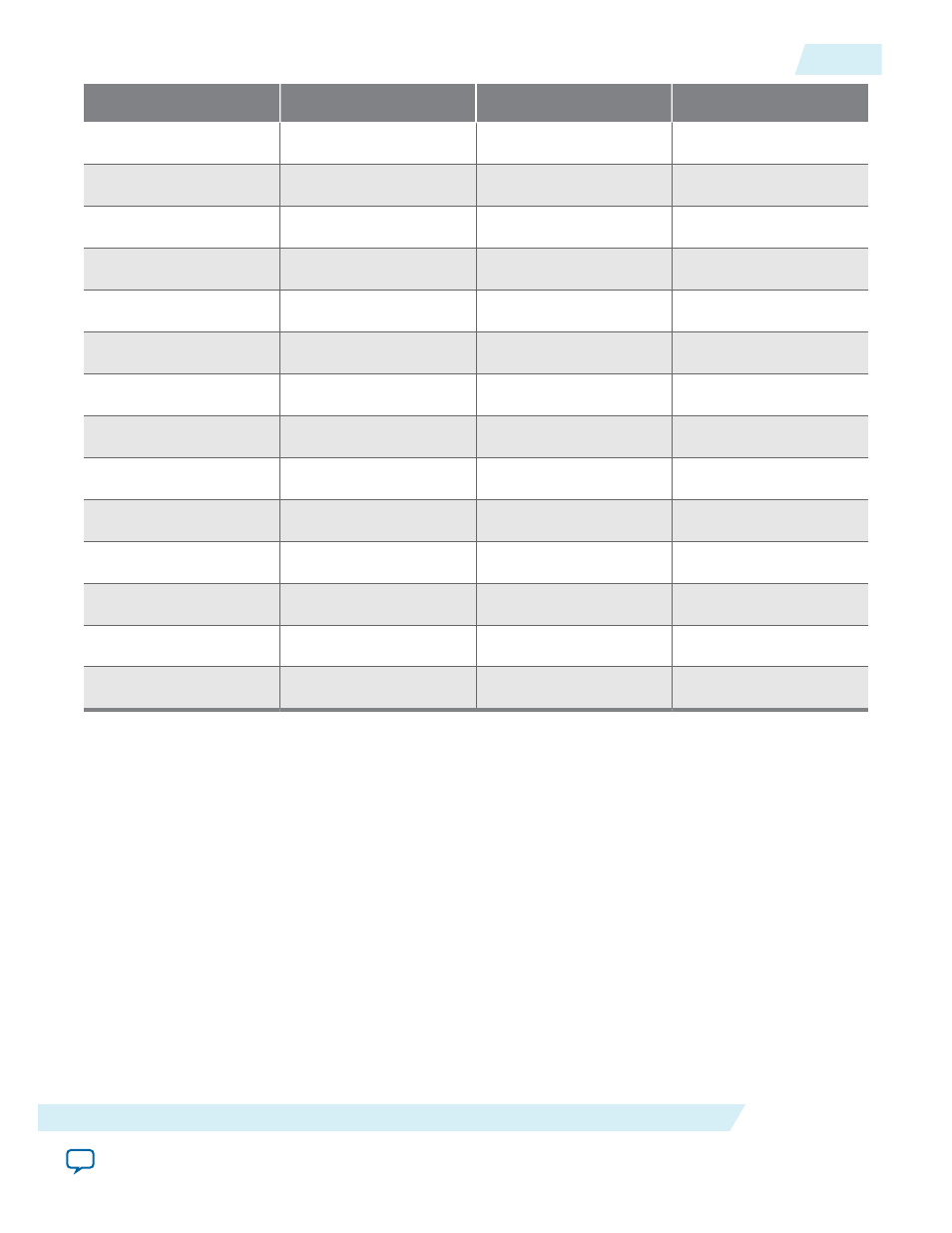

Link Width

Maximum Link Rate

Avalon Interface Width

coreclkout_hip

×8

Gen1

64

250 MHz

×8

Gen1

128

125 MHz

×1

Gen2

64

125 MHz

×2

Gen2

64

125 MHz

×4

Gen2

64

250 MHz

×4

Gen2

128

125 MHz

×8

Gen2

128

250 MHz

×8

Gen2

256

125 MHz

×1

Gen3

64

125 MHz

×2

Gen3

64

125 MHz

×2

Gen3

128

250 MHz

×4

Gen3

128

250 MHz

×4

Gen3

256

125 MHz

×8

Gen3

256

250 MHz

pld_clk

coreclkout_hip

can drive the Application Layer clock along with the

pld_clk

input to the IP core. The

pld_clk

can optionally be sourced by a different clock than

coreclkout_hip

. The

pld_clk

minimum

frequency cannot be lower than the

coreclkout_hip

frequency. Based on specific Application Layer

constraints, a PLL can be used to derive the desired frequency.

Note: For Gen3, Altera recommends using a common reference clock (0 ppm) because when using

separate reference clocks (non 0 ppm), the PCS occasionally must insert SKP symbols, potentially

causing the PCIe link to go to recovery. Gen1 or Gen2 modes are not affected by this issue. Systems

using the common reference clock (0 ppm) are not affected by this issue. The primary repercussion

of this issue is a slight decrease in bandwidth. On Gen3 x8 systems, this bandwidth impact is

negligible. If non 0 ppm mode is required, so that separate reference clocks are used, please contact

Altera for further information and guidance.

UG-01127_avst

2014.12.15

pld_clk

7-7

Reset and Clocks

Altera Corporation